# PCI2050B PCI-to-PCI Bridge

# Data Manual

# **Contents**

| Se | ction  | Title                                      | Page |

|----|--------|--------------------------------------------|------|

| 1  | Introd | uction                                     | 1–1  |

|    | 1.1    | Features                                   | 1–1  |

|    | 1.2    | Related Documents                          | 1–2  |

|    | 1.3    | Trademarks                                 | 1–2  |

|    | 1.4    | Ordering Information                       | 1–2  |

| 2  | Termii | nal Descriptions                           | 2-1  |

| 3  | Featu  | re/Protocol Descriptions                   | 3–1  |

|    | 3.1    | Introduction to the PCI2050B Bridge        | 3–1  |

|    |        | 3.1.1 Write Combining                      | 3–2  |

|    |        | 3.1.2 66-MHz Operation                     | 3–2  |

|    | 3.2    | PCI Commands                               | 3–2  |

|    | 3.3    | Configuration Cycles                       | 3–3  |

|    | 3.4    | Special Cycle Generation                   | 3–5  |

|    | 3.5    | Secondary Clocks                           | 3–5  |

|    | 3.6    | Bus Arbitration                            | 3–6  |

|    |        | 3.6.1 Primary Bus Arbitration              | 3–6  |

|    |        | 3.6.2 Internal Secondary Bus Arbitration   | 3–6  |

|    |        | 3.6.3 External Secondary Bus Arbitration   | 3–7  |

|    | 3.7    | Decode Options                             | 3–7  |

|    | 3.8    | System Error Handling                      | 3–7  |

|    |        | 3.8.1 Posted Write Parity Error            | 3–7  |

|    |        | 3.8.2 Posted Write Time-Out                | 3–7  |

|    |        | 3.8.3 Target Abort on Posted Writes        | 3–7  |

|    |        | 3.8.4 Master Abort on Posted Writes        | 3–8  |

|    |        | 3.8.5 Master Delayed Write Time-Out        | 3–8  |

|    |        | 3.8.6 Master Delayed Read Time-Out         | 3–8  |

|    |        | 3.8.7 Secondary SERR                       | 3–8  |

|    | 3.9    | Parity Handling and Parity Error Reporting | 3–8  |

|    |        | 3.9.1 Address Parity Error                 | 3–8  |

|    |        | 3.9.2 Data Parity Error                    | 3–8  |

|    | 3.10   | Master and Target Abort Handling           | 3–8  |

|    | 3.11   | Discard Timer                              | 3–9  |

|    | 3.12   | Delayed Transactions                       | 3–9  |

|    | 3.13   | Mode Selection                             | 3–9  |

|    | 3.14   | CompactPCI Hot-Swap Support                |      |

|    | 3.15   | JTAG Support                               |      |

|    |        | 3.15.1 Test Port Instructions              | 3_11 |

| Se | ction  | Title                                     | Page |

|----|--------|-------------------------------------------|------|

|    | 3.16   | GPIO Interface                            | 3–15 |

|    |        | 3.16.1 Secondary Clock Mask               | 3–15 |

|    |        | 3.16.2 Transaction Forwarding Control     |      |

|    | 3.17   | PCI Power Management                      | 3–16 |

|    |        | 3.17.1 Behavior in Low-Power States       | 3–16 |

| 4  | Bridge | e Configuration Header                    | 4–1  |

|    | 4.1    | Vendor ID Register                        | 4–2  |

|    | 4.2    | Device ID Register                        | 4–2  |

|    | 4.3    | Command Register                          | 4–3  |

|    | 4.4    | Status Register                           | 4-4  |

|    | 4.5    | Revision ID Register                      | 4–5  |

|    | 4.6    | Class Code Register                       | 4–5  |

|    | 4.7    | Cache Line Size Register                  | 4–5  |

|    | 4.8    | Primary Latency Timer Register            | 4–6  |

|    | 4.9    | Header Type Register                      | 4–6  |

|    | 4.10   | BIST Register                             | 4–6  |

|    | 4.11   | Base Address Register 0                   | 4–7  |

|    | 4.12   | Base Address Register 1                   | 4–7  |

|    | 4.13   | Primary Bus Number Register               | 4–7  |

|    | 4.14   | Secondary Bus Number Register             | 4–8  |

|    | 4.15   | Subordinate Bus Number Register           | 4–8  |

|    | 4.16   | Secondary Bus Latency Timer Register      | 4–8  |

|    | 4.17   | I/O Base Register                         | 4–9  |

|    | 4.18   | I/O Limit Register                        | 4–9  |

|    | 4.19   | Secondary Status Register                 | 4–10 |

|    | 4.20   | Memory Base Register                      | 4-11 |

|    | 4.21   | Memory Limit Register                     | 4-11 |

|    | 4.22   | Prefetchable Memory Base Register         | 4-11 |

|    | 4.23   | Prefetchable Memory Limit Register        | 4-12 |

|    | 4.24   | Prefetchable Base Upper 32 Bits Register  | 4-12 |

|    | 4.25   | Prefetchable Limit Upper 32 Bits Register | 4–13 |

|    | 4.26   | I/O Base Upper 16 Bits Register           |      |

|    | 4.27   | I/O Limit Upper 16 Bits Register          | 4–13 |

|    | 4.28   | Capability Pointer Register               | 4–14 |

|    | 4.29   | Expansion ROM Base Address Register       | 4–14 |

|    | 4.30   | Interrupt Line Register                   | 4–14 |

|    | 4.31   | Interrupt Pin Register                    | 4–15 |

|    | 4.32   | Bridge Control Register                   | 4–15 |

| 5  | Exten  | sion Registers                            | 5–1  |

|    | 5.1    | Chip Control Register                     | 5–1  |

|    | 5.2    | Extended Diagnostic Register              | 5–2  |

|    | 5.3    | Arbiter Control Register                  | 5–3  |

| Se | ection   | Title                                                            | Page         |

|----|----------|------------------------------------------------------------------|--------------|

|    | 5.4      | P_SERR Event Disable Register                                    | 5-4          |

|    | 5.5      | GPIO Output Data Register                                        | 5–5          |

|    | 5.6      | GPIO Output Enable Register                                      | 5–5          |

|    | 5.7      | GPIO Input Data Register                                         | 5–6          |

|    | 5.8      | Secondary Clock Control Register                                 | 5-7          |

|    | 5.9      | P_SERR Status Register                                           | 5–8          |

|    | 5.10     | Power-Management Capability ID Register                          | 5–8          |

|    | 5.11     | Power-Management Next-Item Pointer Register                      | 5–9          |

|    | 5.12     | Power-Management Capabilities Register                           | 5–9          |

|    | 5.13     | Power-Management Control/Status Register                         | 5–10         |

|    | 5.14     | PMCSR Bridge Support Register                                    | 5–11         |

|    | 5.15     | Data Register                                                    | 5–11         |

|    | 5.16     | HS Capability ID Register                                        | 5–12         |

|    | 5.17     | HS Next-Item Pointer Register                                    |              |

|    | 5.18     | Hot-Swap Control Status Register                                 | 5–13         |

|    | 5.19     | Diagnostics Register                                             | 5–14         |

| 6  | Electr   | ical Characteristics                                             | 6–1          |

|    | 6.1      | Absolute Maximum Ratings Over Operating Temperature Ranges .     | 6–1          |

|    | 6.2      | Recommended Operating Conditions                                 | 6–2          |

|    | 6.3      | Electrical Characteristics Over Recommended Operating Conditions | 6–3          |

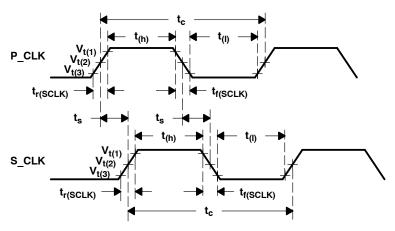

|    | 6.4      | 66-MHz PCI Clock Signal AC Parameters                            |              |

|    | 6.5      | 66-MHz PCI Signal Timing                                         |              |

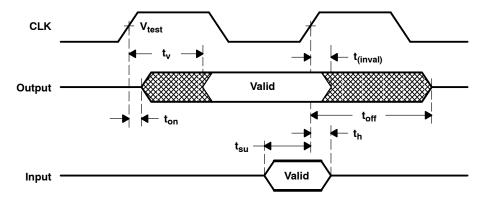

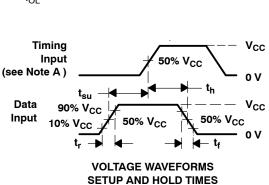

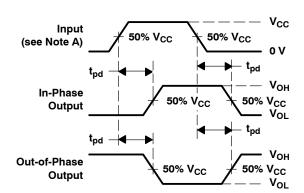

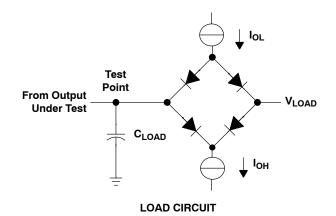

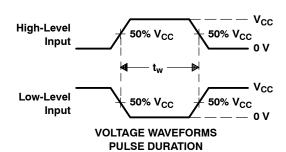

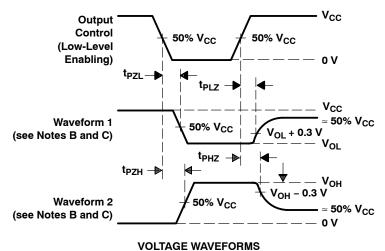

|    | 6.6      | Parameter Measurement Information                                |              |

|    | 6.7      | PCI Bus Parameter Measurement Information                        |              |

| 7  | •        | anical Data                                                      | 7-1          |

| •  | INICCIIC | anicai Dala                                                      | <i>i</i> – i |

# **List of Illustrations**

| Figure | Title                                                             | Page |

|--------|-------------------------------------------------------------------|------|

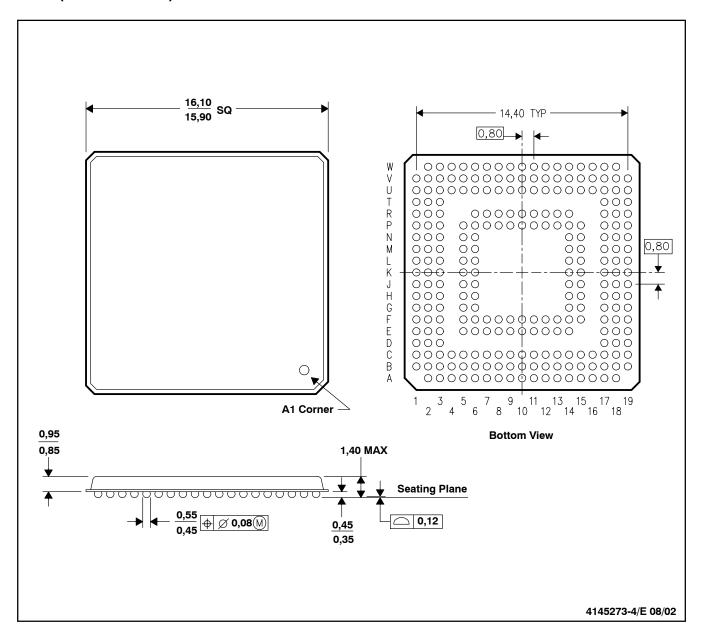

| 2-1    | PCI2050B GHK/ZHK Terminal Diagram                                 | 2–1  |

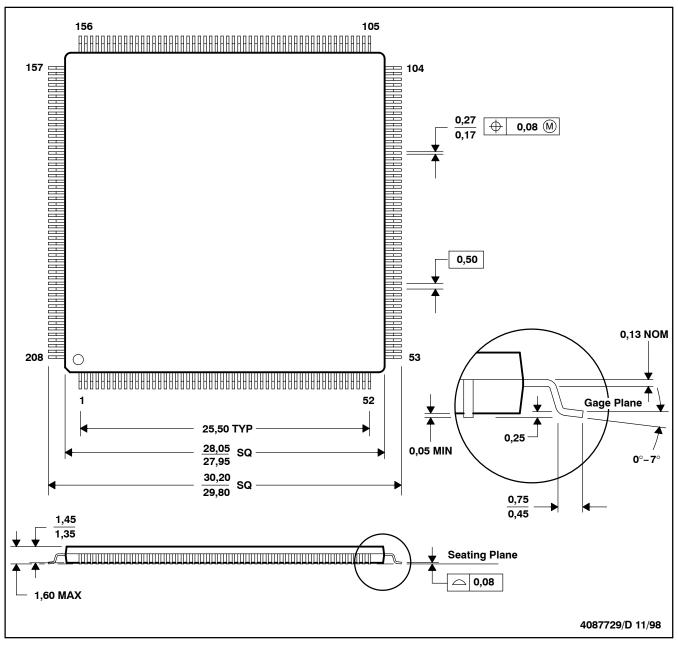

| 2–2    | PCI2050B PDV Terminal Diagram                                     | 2–2  |

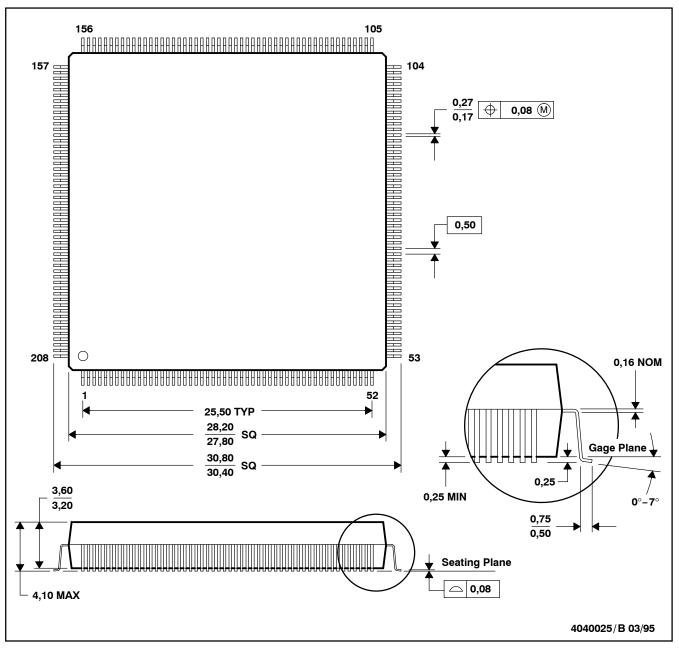

| 2–3    | PCI2050B PPM Terminal Diagram                                     | 2–3  |

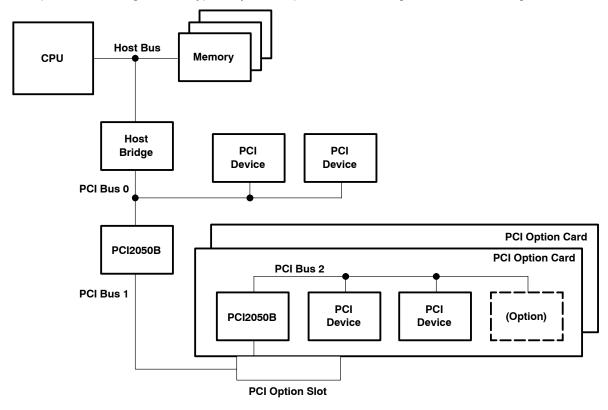

| 3–1    | System Block Diagram                                              | 3–1  |

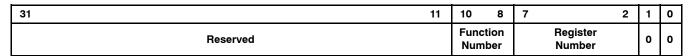

| 3–2    | PCI AD31-AD0 During Address Phase of a Type 0 Configuration Cycle | 3–3  |

| 3–3    | PCI AD31-AD0 During Address Phase of a Type 1 Configuration Cycle | 3–4  |

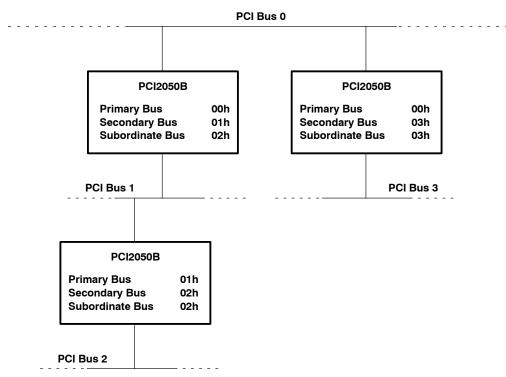

| 3–4    | Bus Hierarchy and Numbering                                       | 3–4  |

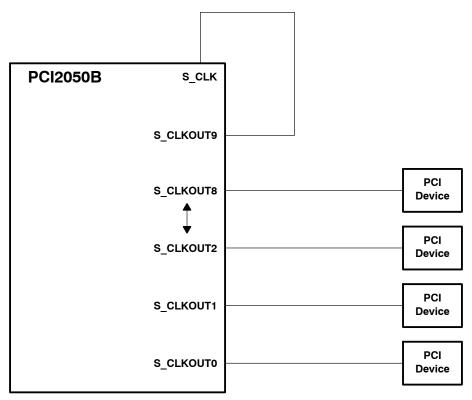

| 3–5    | Secondary Clock Block Diagram                                     | 3–6  |

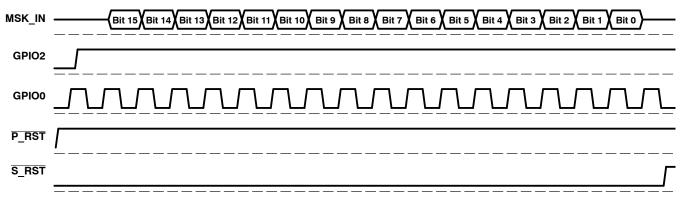

| 3–6    | Clock Mask Read Timing After Reset                                | 3–15 |

| 6–1    | PCI Clock Signal AC Parameter Measurements                        | 6–4  |

| 6–3    | Load Circuit and Voltage Waveforms                                | 6–6  |

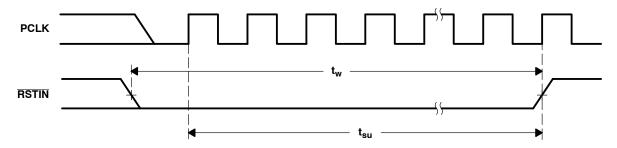

| 6–4    | RSTIN Timing Waveforms                                            | 6–7  |

|        |                                                                   |      |

# **List of Tables**

| Table | Title                                                            | Page |

|-------|------------------------------------------------------------------|------|

| 2–1   | 208-Terminal PDV Signal Names Sorted by Terminal Number          | 2-4  |

| 2-2   | 208-Terminal PPM Signal Names Sorted by Terminal Number          | 2-5  |

| 2-3   | 257-Terminal GHK/ZHK Signal Names Sorted by Terminal Number      | 2-6  |

| 2-4   | 208-Terminal PDV Signal Names Sorted Alphabetically              | 2-8  |

| 2-5   | 208-Terminal PPM Signal Names Sorted Alphabetically              | 2-9  |

| 2-6   | 257-Terminal GHK/ZHK Signal Names Sorted Alphabetically          | 2-10 |

| 2-7   | Primary PCI System Terminals                                     |      |

| 2-8   | Primary PCI Address and Data Terminals                           | 2-12 |

| 2-9   | Primary PCI Interface Control Terminals                          |      |

| 2–10  | Secondary PCI System Terminals                                   |      |

| 2–11  | Secondary PCI Address and Data Terminals                         |      |

| 2-12  | Secondary PCI Interface Control Terminals                        |      |

| 2–13  | JTAG Interface Terminals                                         | 2-16 |

| 2–14  | Miscellaneous Terminals                                          | 2-17 |

| 2-15  | Power Supply Terminals                                           | 2-17 |

| 3–1   | PCI Command Definitions                                          | 3–3  |

| 3–2   | PCI S_AD31-S_AD16 During the Address Phase of a Type 0 Configura |      |

|       | Cycle                                                            |      |

| 3–3   | Configuration via MS0 and MS1                                    |      |

| 3–4   | JTAG Instructions and Op Codes                                   |      |

| 3–5   | Boundary Scan Terminal Order                                     |      |

| 3–6   | Clock Mask Data Format                                           |      |

| 4–1   | Bridge Configuration Header                                      |      |

| 4–2   | Command Register Description                                     |      |

| 4–3   | Status Register Description                                      |      |

| 4–4   | Secondary Status Register Description                            |      |

| 4–5   | Bridge Control Register Description                              |      |

| 5–1   | Chip Control Register Description                                |      |

| 5–2   | Extended Diagnostic Register Description                         |      |

| 5–3   | Arbiter Control Register Description                             |      |

| 5–4   | P_SERR Event Disable Register Description                        |      |

| 5–5   | GPIO Output Data Register Description                            | 5–5  |

| 5–6   | GPIO Output Enable Register Description                          | 5–5  |

| 5–7   | GPIO Input Data Register Description                             | 5–6  |

| 5–8   | Secondary Clock Control Register Description                     | 5–7  |

| 5–9   | P_SERR Status Register Description                               | 5–8  |

| 5–10  | Power-Management Capabilities Register Description               | 5–9  |

| 5–11  | Power-Management Control/Status Register                         | 5-10 |

| Table | Title                                        | Page |

|-------|----------------------------------------------|------|

| 5–12  | PMCSR Bridge Support Register Description    | 5–11 |

| 5–13  | Hot-Swap Control Status Register Description | 5–13 |

| 5–14  | Diagnostics Register Description             | 5-14 |

#### 1 Introduction

The Texas Instruments PCI2050B PCI-to-PCI bridge provides a high performance connection path between two peripheral component interconnect (PCI) buses operating at a maximum bus frequency of 66-MHz. Transactions occur between masters on one and targets on another PCI bus, and the PCI2050B bridge allows bridged transactions to occur concurrently on both buses. The bridge supports burst mode transfers to maximize data throughput, and the two bus traffic paths through the bridge act independently.

The PCI2050B bridge is compliant with the PCI Local Bus Specification, and can be used to overcome the electrical loading limits of 10 devices per PCI bus and one PCI device per extension slot by creating hierarchical buses. The PCI2050B provides two-tier internal arbitration for up to nine secondary bus masters and may be implemented with an external bus arbiter.

The CompactPCI™ hot-swap extended PCI capability makes the PCI2050B bridge an ideal solution for multifunction compact PCI cards and adapting single function cards to hot-swap compliance.

The PCI2050B bridge is compliant with the *PCI-to-PCI Bridge Specification* (Revision 1.1). The PCI2050B bridge provides compliance for *PCI Bus Power Management Interface Specification* (Revision 1.1). The PCI2050B bridge has been designed to lead the industry in power conservation and data throughput. An advanced CMOS process achieves low system power consumption while operating at PCI clock rates up to 66-MHz.

#### 1.1 Features

The PCI2050B bridge supports the following features:

- Two 32-bit, 66-MHz PCI buses

- 3.3-V core logic with universal PCI interfaces compatible with 3.3-V and 5-V PCI signaling environments

- Internal two-tier arbitration for up to nine secondary bus masters and supports an external secondary bus arbiter

- Ten secondary PCI clock outputs

- Independent read and write buffers for each direction

- Burst data transfers with pipeline architecture to maximize data throughput in both directions

- Supports write combing for enhanced data throughput

- Up to three delayed transactions in both directions

- Supports the frame-to-frame delay of only four PCI clocks from one bus to another

- · Bus locking propagation

- Predictable latency per PCI Local Bus Specification

- Architecture configurable for PCI Bus Power Management Interface Specification

- CompactPCI hot-swap functionality

- · Secondary bus is driven low during reset

- VGA/palette memory and I/O decoding options

- Advanced submicron, low-power CMOS technology

- 208-terminal PDV, 208-terminal PPM, or 257-terminal MicroStar BGA™ package

#### 1.2 Related Documents

- Advanced Configuration and Power Interface (ACPI) Specification (Revision 1.0)

- IEEE Standard Test Access Port and Boundary-Scan Architecture

- PCI Local Bus Specification (Revision 2.2)

- PCI-to-PCI Bridge Specification (Revision 1.1)

- PCI Bus Power Management Interface Specification (Revision 1.1)

- PICMG CompactPCI Hot-Swap Specification (Revision 1.0)

#### 1.3 Trademarks

CompactPCI is a trademark of PICMG - PCI Industrial Computer Manufacturers Group, Inc.

Intel is a trademark of Intel Corporation.

MicroStar BGA and TI are trademarks of Texas Instruments.

Other trademarks are the property of their respective owners.

# 1.4 Ordering Information

| ORDERING NUMBER | VOLTAGE                  | TEMPERATURE   | PACKAGE      |

|-----------------|--------------------------|---------------|--------------|

| PCI2050BPDV     | 3.3-V, 5-V Tolerant I/Os | 0°C to 70°C   | 208 QFP      |

| PCI2050BPPM     | 3.3-V, 5-V Tolerant I/Os | 0°C to 70°C   | 208 QFP      |

| PCI2050BGHK     | 3.3-V, 5-V Tolerant I/Os | 0°C to 70°C   | 257 BGA      |

| PCI2050BZHK     | 3.3-V, 5-V Tolerant I/Os | 0°C to 70°C   | 257 RoHS BGA |

| PCI2050BIPDV    | 3.3-V, 5-V Tolerant I/Os | −40°C to 85°C | 208 QFP      |

| PCI2050BIGHK    | 3.3-V, 5-V Tolerant I/Os | −40°C to 85°C | 257 BGA      |

| PCI2050BIZHK    | 3.3-V, 5-V Tolerant I/Os | −40°C to 85°C | 257 RoHS BGA |

# 2 Terminal Descriptions

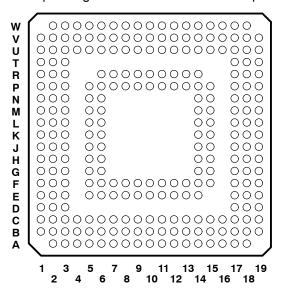

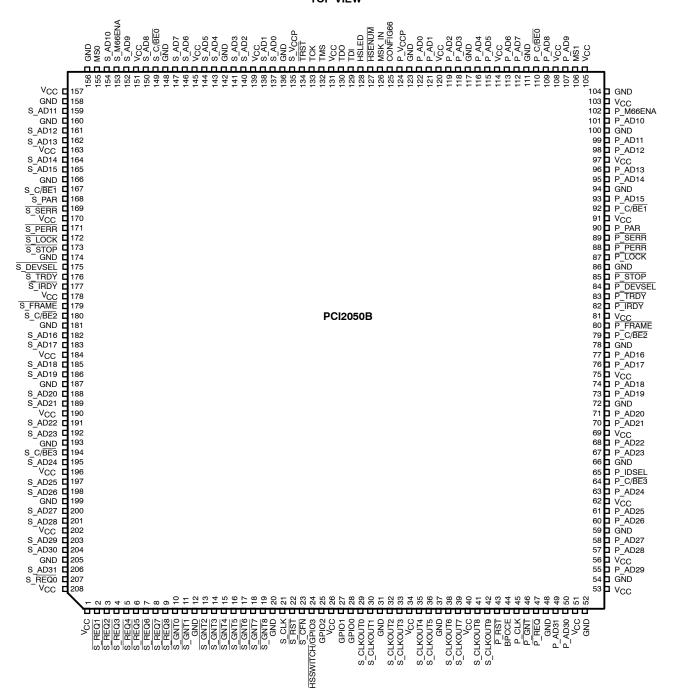

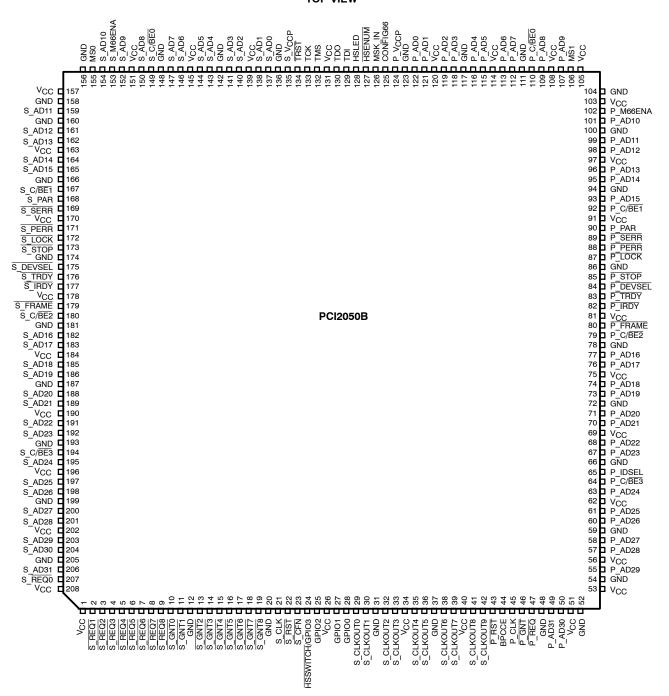

The PCI2050B device is available in four packages, a 257-terminal GHK MicroStar BGA™ package, a 257-terminal RoHS-compliant ZHK MicroStar BGA™ package, a 208-terminal PDV package, or a 208-terminal PPM package. The GHK and ZHK packages are mechanically and electrically identical, but the ZHK is a RoHS-compliant design. Throughout the remainder of this manual, only the GHK package designator is used for either the GHK or the ZHK package. Figure 2–1 is the GHK-package terminal diagram. Figure 2–2 is the PDV-package terminal diagram. Figure 2–3 is the PPM-package terminal diagram. Table 2–1 lists terminals on the PDV packaged device in increasing numerical order with the signal name for each. Table 2–2 lists terminals on the PPM packaged device in increasing alphanumerical order with the signal name for each. Table 2–3 lists terminals on the GHK packaged device in increasing alphanumerical order with the signal name for each. Table 2–4, Table 2–5, and Table 2–6 list the signal names in alphabetical order, with corresponding terminal numbers for each package type.

Figure 2-1. PCI2050B GHK/ZHK Terminal Diagram

# PDV LOW-PROFILE QUAD FLAT PACKAGE TOP VIEW

Figure 2-2. PCI2050B PDV Terminal Diagram

# PPM QUAD FLAT PACKAGE TOP VIEW

Figure 2-3. PCI2050B PPM Terminal Diagram

Table 2–1. 208-Terminal PDV Signal Names Sorted by Terminal Number

| PDV<br>NO. | SIGNAL NAME     | PDV<br>NO. | SIGNAL NAME     | PDV<br>NO. | SIGNAL NAME        | PDV<br>NO. | SIGNAL NAME        | PDV<br>NO. | SIGNAL NAME     |

|------------|-----------------|------------|-----------------|------------|--------------------|------------|--------------------|------------|-----------------|

| 1          | V <sub>CC</sub> | 43         | P_RST           | 85         | P_STOP             | 127        | HS_ENUM            | 169        | S_SERR          |

| 2          | S_REQ1          | 44         | BPCCE           | 86         | GND                | 128        | HS_LED             | 170        | V <sub>CC</sub> |

| 3          | S_REQ2          | 45         | P_CLK           | 87         | P_LOCK             | 129        | TDI                | 171        | S_PERR          |

| 4          | S_REQ3          | 46         | P_GNT           | 88         | P_PERR             | 130        | TDO                | 172        | S_LOCK          |

| 5          | S_REQ4          | 47         | P_REQ           | 89         | P_SERR             | 131        | V <sub>CC</sub>    | 173        | S_STOP          |

| 6          | S_REQ5          | 48         | GND             | 90         | P_PAR              | 132        | TMS                | 174        | GND             |

| 7          | S_REQ6          | 49         | P_AD31          | 91         | V <sub>CC</sub>    | 133        | TCK                | 175        | S_DEVSEL        |

| 8          | S_REQ7          | 50         | P_AD30          | 92         | P_C/BE1            | 134        | TRST               | 176        | S_TRDY          |

| 9          | S_REQ8          | 51         | V <sub>CC</sub> | 93         | P_AD15             | 135        | S_V <sub>CCP</sub> | 177        | S_IRDY          |

| 10         | S_GNT0          | 52         | GND             | 94         | GND                | 136        | GND                | 178        | $V_{CC}$        |

| 11         | S_GNT1          | 53         | V <sub>CC</sub> | 95         | P_AD14             | 137        | S_AD0              | 179        | S_FRAME         |

| 12         | GND             | 54         | GND             | 96         | P_AD13             | 138        | S_AD1              | 180        | S_C/BE2         |

| 13         | S_GNT2          | 55         | P_AD29          | 97         | V <sub>CC</sub>    | 139        | V <sub>CC</sub>    | 181        | GND             |

| 14         | S_GNT3          | 56         | V <sub>CC</sub> | 98         | P_AD12             | 140        | S_AD2              | 182        | S_AD16          |

| 15         | S_GNT4          | 57         | P_AD28          | 99         | P_AD11             | 141        | S_AD3              | 183        | S_AD17          |

| 16         | S_GNT5          | 58         | P_AD27          | 100        | GND                | 142        | GND                | 184        | V <sub>CC</sub> |

| 17         | S_GNT6          | 59         | GND             | 101        | P_AD10             | 143        | S_AD4              | 185        | S_AD18          |

| 18         | S_GNT7          | 60         | P_AD26          | 102        | P_M66ENA           | 144        | S_AD5              | 186        | S_AD19          |

| 19         | S_GNT8          | 61         | P_AD25          | 103        | V <sub>CC</sub>    | 145        | V <sub>CC</sub>    | 187        | GND             |

| 20         | GND             | 62         | V <sub>CC</sub> | 104        | GND                | 146        | S_AD6              | 188        | S_AD20          |

| 21         | S_CLK           | 63         | P_AD24          | 105        | V <sub>CC</sub>    | 147        | S_AD7              | 189        | S_AD21          |

| 22         | S_RST           | 64         | P_C/BE3         | 106        | MS1                | 148        | GND                | 190        | V <sub>CC</sub> |

| 23         | S_CFN           | 65         | P_IDSEL         | 107        | P_AD9              | 149        | S_C/BE0            | 191        | S_AD22          |

| 24         | HS_SWITCH/GPIO3 | 66         | GND             | 108        | V <sub>CC</sub>    | 150        | S_AD8              | 192        | S_AD23          |

| 25         | GPIO2           | 67         | P_AD23          | 109        | P_AD8              | 151        | V <sub>CC</sub>    | 193        | GND             |

| 26         | V <sub>CC</sub> | 68         | P_AD22          | 110        | P_C/BE0            | 152        | S_AD9              | 194        | S_C/BE3         |

| 27         | GPIO1           | 69         | V <sub>CC</sub> | 111        | GND                | 153        | S_M66ENA           | 195        | S_AD24          |

| 28         | GPIO0           | 70         | P_AD21          | 112        | P_AD7              | 154        | S_AD10             | 196        | V <sub>CC</sub> |

| 29         | S_CLKOUT0       | 71         | P_AD20          | 113        | P_AD6              | 155        | MS0                | 197        | S_AD25          |

| 30         | S_CLKOUT1       | 72         | GND             | 114        | V <sub>CC</sub>    | 156        | GND                | 198        | S_AD26          |

| 31         | GND             | 73         | P_AD19          | 115        | P_AD5              | 157        | V <sub>CC</sub>    | 199        | GND             |

| 32         | S_CLKOUT2       | 74         | P_AD18          | 116        | P_AD4              | 158        | GND                | 200        | S_AD27          |

| 33         | S_CLKOUT3       | 75         | V <sub>CC</sub> | 117        | GND                | 159        | S_AD11             | 201        | S_AD28          |

| 34         | V <sub>CC</sub> | 76         | P_AD17          | 118        | P_AD3              | 160        | GND                | 202        | V <sub>CC</sub> |

| 35         | S_CLKOUT4       | 77         | P_AD16          | 119        | P_AD2              | 161        | S_AD12             | 203        | S_AD29          |

| 36         | S_CLKOUT5       | 78         | GND             | 120        | V <sub>CC</sub>    | 162        | S_AD13             | 204        | S_AD30          |

| 37         | GND             | 79         | P_C/BE2         | 121        | P_AD1              | 163        | V <sub>CC</sub>    | 205        | GND             |

| 38         | S_CLKOUT6       | 80         | P_FRAME         | 122        | P_AD0              | 164        | S_AD14             | 206        | S_AD31          |

| 39         | S_CLKOUT7       | 81         | V <sub>CC</sub> | 123        | GND                | 165        | S_AD15             | 207        | S_REQ0          |

| 40         | V <sub>CC</sub> | 82         | P_IRDY          | 124        | P_V <sub>CCP</sub> | 166        | GND                | 208        | $V_{CC}$        |

| 41         | S_CLKOUT8       | 83         | P_TRDY          | 125        | CONFIG66           | 167        | S_C/BE1            |            |                 |

| 42         | S_CLKOUT9       | 84         | P_DEVSEL        | 126        | MSK_IN             | 168        | S_PAR              |            |                 |

Table 2–2. 208-Terminal PPM Signal Names Sorted by Terminal Number

| PPM<br>NO. | SIGNAL NAME     | PPM<br>NO. | SIGNAL NAME     | PPM<br>NO. | SIGNAL NAME        | PPM<br>NO. | SIGNAL NAME        | PPM<br>NO. | SIGNAL NAME     |

|------------|-----------------|------------|-----------------|------------|--------------------|------------|--------------------|------------|-----------------|

| 1          | V <sub>CC</sub> | 43         | P_RST           | 85         | P_STOP             | 127        | HS_ENUM            | 169        | S_SERR          |

| 2          | S_REQ1          | 44         | BPCCE           | 86         | GND                | 128        | HS_LED             | 170        | V <sub>CC</sub> |

| 3          | S_REQ2          | 45         | P_CLK           | 87         | P_LOCK             | 129        | TDI                | 171        | S_PERR          |

| 4          | S_REQ3          | 46         | P_GNT           | 88         | P_PERR             | 130        | TDO                | 172        | S_LOCK          |

| 5          | S_REQ4          | 47         | P_REQ           | 89         | P_SERR             | 131        | V <sub>CC</sub>    | 173        | S_STOP          |

| 6          | S_REQ5          | 48         | GND             | 90         | P_PAR              | 132        | TMS                | 174        | GND             |

| 7          | S_REQ6          | 49         | P_AD31          | 91         | V <sub>CC</sub>    | 133        | TCK                | 175        | S_DEVSEL        |

| 8          | S_REQ7          | 50         | P_AD30          | 92         | P_C/BE1            | 134        | TRST               | 176        | S_TRDY          |

| 9          | S_REQ8          | 51         | V <sub>CC</sub> | 93         | P_AD15             | 135        | S_V <sub>CCP</sub> | 177        | S_IRDY          |

| 10         | S_GNT0          | 52         | GND             | 94         | GND                | 136        | GND                | 178        | V <sub>CC</sub> |

| 11         | S_GNT1          | 53         | V <sub>CC</sub> | 95         | P_AD14             | 137        | S_AD0              | 179        | S_FRAME         |

| 12         | GND             | 54         | GND             | 96         | P_AD13             | 138        | S_AD1              | 180        | S_C/BE2         |

| 13         | S_GNT2          | 55         | P_AD29          | 97         | V <sub>CC</sub>    | 139        | V <sub>CC</sub>    | 181        | GND             |

| 14         | S_GNT3          | 56         | V <sub>CC</sub> | 98         | P_AD12             | 140        | S_AD2              | 182        | S_AD16          |

| 15         | S_GNT4          | 57         | P_AD28          | 99         | P_AD11             | 141        | S_AD3              | 183        | S_AD17          |

| 16         | S_GNT5          | 58         | P_AD27          | 100        | GND                | 142        | GND                | 184        | V <sub>CC</sub> |

| 17         | S_GNT6          | 59         | GND             | 101        | P_AD10             | 143        | S_AD4              | 185        | S_AD18          |

| 18         | S_GNT7          | 60         | P_AD26          | 102        | P_M66ENA           | 144        | S_AD5              | 186        | S_AD19          |

| 19         | S_GNT8          | 61         | P_AD25          | 103        | V <sub>CC</sub>    | 145        | V <sub>CC</sub>    | 187        | GND             |

| 20         | GND             | 62         | V <sub>CC</sub> | 104        | GND                | 146        | S_AD6              | 188        | S_AD20          |

| 21         | S_CLK           | 63         | P_AD24          | 105        | V <sub>CC</sub>    | 147        | S_AD7              | 189        | S_AD21          |

| 22         | S_RST           | 64         | P_C/BE3         | 106        | MS1                | 148        | GND                | 190        | V <sub>CC</sub> |

| 23         | S_CFN           | 65         | P_IDSEL         | 107        | P_AD9              | 149        | S_C/BE0            | 191        | S_AD22          |

| 24         | HS_SWITCH/GPIO3 | 66         | GND             | 108        | V <sub>CC</sub>    | 150        | S_AD8              | 192        | S_AD23          |

| 25         | GPIO2           | 67         | P_AD23          | 109        | P_AD8              | 151        | V <sub>CC</sub>    | 193        | GND             |

| 26         | V <sub>CC</sub> | 68         | P_AD22          | 110        | P_C/BE0            | 152        | S_AD9              | 194        | S_C/BE3         |

| 27         | GPI01           | 69         | V <sub>CC</sub> | 111        | GND                | 153        | S_M66ENA           | 195        | S_AD24          |

| 28         | GPI00           | 70         | P_AD21          | 112        | P_AD7              | 154        | S_AD10             | 196        | V <sub>CC</sub> |

| 29         | S_CLKOUT0       | 71         | P_AD20          | 113        | P_AD6              | 155        | MS0                | 197        | S_AD25          |

| 30         | S_CLKOUT1       | 72         | GND             | 114        | V <sub>CC</sub>    | 156        | GND                | 198        | S_AD26          |

| 31         | GND             | 73         | P_AD19          | 115        | P_AD5              | 157        | V <sub>CC</sub>    | 199        | GND             |

| 32         | S_CLKOUT2       | 74         | P_AD18          | 116        | P_AD4              | 158        | GND                | 200        | S_AD27          |

| 33         | S_CLKOUT3       | 75         | V <sub>CC</sub> | 117        | GND                | 159        | S_AD11             | 201        | S_AD28          |

| 34         | V <sub>CC</sub> | 76         | P_AD17          | 118        | P_AD3              | 160        | GND                | 202        | V <sub>CC</sub> |

| 35         | S_CLKOUT4       | 77         | P_AD16          | 119        | P_AD2              | 161        | S_AD12             | 203        | S_AD29          |

| 36         | S_CLKOUT5       | 78         | GND             | 120        | V <sub>CC</sub>    | 162        | S_AD13             | 204        | S_AD30          |

| 37         | GND             | 79         | P_C/BE2         | 121        | P_AD1              | 163        | V <sub>CC</sub>    | 205        | GND             |

| 38         | S_CLKOUT6       | 80         | P_FRAME         | 122        | P_AD0              | 164        | S_AD14             | 206        | S_AD31          |

| 39         | S_CLKOUT7       | 81         | V <sub>CC</sub> | 123        | GND                | 165        | S_AD15             | 207        | S_REQ0          |

| 40         | V <sub>CC</sub> | 82         | P_IRDY          | 124        | P_V <sub>CCP</sub> | 166        | GND                | 208        | V <sub>CC</sub> |

| 41         | S_CLKOUT8       | 83         | P_TRDY          | 125        | CONFIG66           | 167        | S_C/BE1            |            |                 |

| 42         | S_CLKOUT9       | 84         | P_DEVSEL        | 126        | MSK_IN             | 168        | S_PAR              |            |                 |

Table 2-3. 257-Terminal GHK/ZHK Signal Names Sorted by Terminal Number

| GHK |                 | GHK             |                 | GHK | N Signal Names C   | GHK | -                  | GHK |                 |

|-----|-----------------|-----------------|-----------------|-----|--------------------|-----|--------------------|-----|-----------------|

| NO. | SIGNAL NAME     | NO.             | SIGNAL NAME     | NO. | SIGNAL NAME        | NO. | SIGNAL NAME        | NO. | SIGNAL NAME     |

| A2  | NC              | C8              | V <sub>CC</sub> | F11 | S_FRAME            | K14 | TMS                | P10 | P_C/BE2         |

| A3  | V <sub>CC</sub> | C9              | S_AD18          | F12 | S_C/BE1            | K15 | V <sub>CC</sub>    | P11 | P_TRDY          |

| A4  | S_AD31          | C10             | NC              | F13 | GND                | K17 | TDO                | P12 | P_LOCK          |

| A5  | S_AD28          | C11             | S_IRDY          | F14 | S_AD9              | K18 | TDI                | P13 | P_C/BE1         |

| A6  | S_AD25          | C12             | S_LOCK          | F15 | S_AD10             | K19 | NC                 | P14 | P_AD12          |

| A7  | GND             | C13             | S_PAR           | F17 | S_AD8              | L1  | S_CLKOUT0          | P15 | $V_{CC}$        |

| A8  | S_AD20          | C14             | V <sub>CC</sub> | F18 | GND                | L2  | S_CLKOUT1          | P17 | P_AD7           |

| A9  | V <sub>CC</sub> | C15             | GND             | F19 | S_AD7              | L3  | NC                 | P18 | P_AD6           |

| A10 | S_C/BE2         | C16             | NC              | G1  | S_GNT3             | L5  | S_CLKOUT2          | P19 | P_AD5           |

| A11 | S_DEVSEL        | C17             | NC              | G2  | S_GNT2             | L6  | GND                | R1  | P_GNT           |

| A12 | GND             | C18             | NC              | G3  | GND                | L14 | HS_LED             | R2  | NC              |

| A13 | $V_{CC}$        | C19             | NC              | G5  | S_REQ8             | L15 | HS_ENUM            | R3  | P_AD31          |

| A14 | GND             | D1              | NC              | G6  | S_REQ3             | L17 | MSK_IN             | R6  | P_AD29          |

| A15 | S_AD13          | D2              | V <sub>CC</sub> | G14 | S_AD6              | L18 | CONFIG66           | R7  | P_AD26          |

| A16 | V <sub>CC</sub> | D3              | NC              | G15 | S_C/BE0            | L19 | P_V <sub>CCP</sub> | R8  | GND             |

| A17 | NC              | D17             | NC              | G17 | V <sub>CC</sub>    | M1  | S_CLKOUT3          | R9  | P_AD19          |

| A18 | NC              | D18             | NC              | G18 | S_AD5              | M2  | $V_{CC}$           | R10 | GND             |

| B1  | NC              | D19             | GND             | G19 | S_AD4              | МЗ  | S_CLKOUT4          | R11 | P_DEVSEL        |

| B2  | NC              | E1              | S_REQ5          | H1  | S_GNT7             | M5  | GND                | R12 | P_PERR          |

| В3  | NC              | E2              | S_REQ4          | H2  | S_GNT6             | М6  | S_CLKOUT5          | R13 | P_AD14          |

| B4  | S_REQ0          | E3              | S_REQ1          | НЗ  | S_GNT5             | M14 | P_AD4              | R14 | GND             |

| B5  | S_AD29          | E5 <sup>†</sup> | NC              | H5  | S_GNT4             | M15 | $V_{CC}$           | R17 | P_AD9           |

| B6  | S_AD26          | E6              | S_AD30          | H6  | S_GNT1             | M17 | P_AD1              | R18 | P_C/BE0         |

| В7  | S_C/BE3         | E7              | GND             | H14 | S_AD3              | M18 | P_AD0              | R19 | GND             |

| B8  | S_AD21          | E8              | S_AD23          | H15 | GND                | M19 | GND                | T1  | P_AD30          |

| B9  | NC              | E9              | GND             | H17 | S_AD2              | N1  | S_CLKOUT6          | T2  | V <sub>CC</sub> |

| B10 | GND             | E10             | S_AD16          | H18 | V <sub>CC</sub>    | N2  | S_CLKOUT7          | T3  | NC              |

| B11 | S_TRDY          | E11             | V <sub>CC</sub> | H19 | S_AD1              | N3  | V <sub>CC</sub>    | T17 | NC              |

| B12 | S_STOP          | E12             | S_PERR          | J1  | S_GNT8             | N5  | BPCCE              | T18 | $V_{CC}$        |

| B13 | S_SERR          | E13             | S_AD15          | J2  | GND                | N6  | S_CLKOUT8          | T19 | MS1             |

| B14 | S_AD14          | E14             | S_AD11          | J3  | S_CLK              | N14 | P_AD8              | U1  | GND             |

| B15 | S_AD12          | E17             | MS0             | J5  | S_RST              | N15 | V <sub>CC</sub>    | U2  | NC              |

| B16 | NC              | E18             | S_M66ENA        | J6  | S_CFN              | N17 | GND                | U3  | NC              |

| B17 | NC              | E19             | V <sub>CC</sub> | J14 | GND                | N18 | P_AD3              | U4  | NC              |

| B18 | NC              | F1              | S_GNT0          | J15 | S_AD0              | N19 | P_AD2              | U5  | GND             |

| B19 | NC              | F2              | S_REQ7          | J17 | S_V <sub>CCP</sub> | P1  | S_CLKOUT9          | U6  | P_AD27          |

| C1  | NC              | F3              | S_REQ6          | J18 | TRST               | P2  | P_RST              | U7  | P_AD24          |

| C2  | NC              | F5              | S_REQ2          | J19 | TCK                | P3  | P_CLK              | U8  | P_AD23          |

| СЗ  | NC              | F6              | V <sub>CC</sub> | K1  | HS_SWITCH/GPIO3    | P5  | GND                | U9  | GND             |

| C4  | NC              | F7              | V <sub>CC</sub> | K2  | GPIO2              | P6  | P_REQ              | U10 | P_AD16          |

| C5  | GND             | F8              | S_AD22          | КЗ  | V <sub>CC</sub>    | P7  | V <sub>CC</sub>    | U11 | P_IRDY          |

| C6  | S_AD27          | F9              | S_AD19          | K5  | GPIO1              | P8  | V <sub>CC</sub>    | U12 | GND             |

| C7  | S_AD24          | F10             | S_AD17          | K6  | GPIO0              | P9  | P_AD18             | U13 | V <sub>CC</sub> |

$<sup>^\</sup>dagger$  Terminal E5 is used as a key to indicate the location of the A1 corner. It is a no-connect terminal.

Table 2–3. 257-Terminal GHK/ZHK Signal Names Sorted by Terminal Number (Continued)

| GHK<br>NO. | SIGNAL NAME | GHK<br>NO. | SIGNAL NAME | GHK<br>NO. | SIGNAL NAME     | GHK<br>NO. | SIGNAL NAME     | GHK<br>NO. | SIGNAL NAME |

|------------|-------------|------------|-------------|------------|-----------------|------------|-----------------|------------|-------------|

| U14        | P_AD13      | V4         | NC          | V13        | P_PAR           | W4         | V <sub>CC</sub> | W13        | P_SERR      |

| U15        | P_AD10      | V5         | NC          | V14        | GND             | W5         | P_AD28          | W14        | P_AD15      |

| U16        | NC          | V6         | GND         | V15        | P_AD11          | W6         | P_AD25          | W15        | $V_{CC}$    |

| U17        | NC          | V7         | P_C/BE3     | V16        | V <sub>CC</sub> | W7         | P_IDSEL         | W16        | P_M66ENA    |

| U18        | NC          | V8         | P_AD22      | V17        | NC              | W8         | V <sub>CC</sub> | W17        | NC          |

| U19        | NC          | V9         | P_AD20      | V18        | NC              | W9         | P_AD21          | W18        | NC          |

| V1         | NC          | V10        | P_AD17      | V19        | NC              | W10        | $V_{CC}$        |            |             |

| V2         | NC          | V11        | $V_{CC}$    | W2         | NC              | W11        | P_FRAME         |            |             |

| V3         | NC          | V12        | NC          | W3         | NC              | W12        | P_STOP          |            |             |

Table 2-4. 208-Terminal PDV Signal Names Sorted Alphabetically

| SIGNAL NAME     | PDV<br>NO. | SIGNAL NAME | PDV<br>NO. | SIGNAL NAME        | PDV<br>NO. | SIGNAL NAME | PDV<br>NO. | SIGNAL NAME        | PDV<br>NO. |

|-----------------|------------|-------------|------------|--------------------|------------|-------------|------------|--------------------|------------|

| BPCCE           | 44         | P_AD0       | 122        | P_LOCK             | 87         | S_C/BE0     | 149        | S_SERR             | 169        |

| CONFIG66        | 125        | P_AD1       | 121        | P_M66ENA           | 102        | S_C/BE1     | 167        | S_STOP             | 173        |

| GND             | 12         | P_AD2       | 119        | P_PAR              | 90         | S_C/BE2     | 180        | S_TRDY             | 176        |

| GND             | 20         | P_AD3       | 118        | P_PERR             | 88         | S_C/BE3     | 194        | S_V <sub>CCP</sub> | 135        |

| GND             | 31         | P_AD4       | 116        | P_REQ              | 47         | S_CFN       | 23         | TCK                | 133        |

| GND             | 37         | P_AD5       | 115        | P_RST              | 43         | S_CLK       | 21         | TDI                | 129        |

| GND             | 48         | P_AD6       | 113        | P_SERR             | 89         | S_CLKOUT0   | 29         | TDO                | 130        |

| GND             | 52         | P_AD7       | 112        | P_STOP             | 85         | S_CLKOUT1   | 30         | TMS                | 132        |

| GND             | 54         | P_AD8       | 109        | P_TRDY             | 83         | S_CLKOUT2   | 32         | TRST               | 134        |

| GND             | 59         | P_AD9       | 107        | P_V <sub>CCP</sub> | 124        | S_CLKOUT3   | 33         | $V_{CC}$           | 1          |

| GND             | 66         | P_AD10      | 101        | S_AD0              | 137        | S_CLKOUT4   | 35         | $V_{CC}$           | 26         |

| GND             | 72         | P_AD11      | 99         | S_AD1              | 138        | S_CLKOUT5   | 36         | $V_{CC}$           | 34         |

| GND             | 78         | P_AD12      | 98         | S_AD2              | 140        | S_CLKOUT6   | 38         | $V_{CC}$           | 40         |

| GND             | 86         | P_AD13      | 96         | S_AD3              | 141        | S_CLKOUT7   | 39         | V <sub>CC</sub>    | 51         |

| GND             | 94         | P_AD14      | 95         | S_AD4              | 143        | S_CLKOUT8   | 41         | $V_{CC}$           | 53         |

| GND             | 100        | P_AD15      | 93         | S_AD5              | 144        | S_CLKOUT9   | 42         | $V_{CC}$           | 56         |

| GND             | 104        | P_AD16      | 77         | S_AD6              | 146        | S_DEVSEL    | 175        | $V_{CC}$           | 62         |

| GND             | 111        | P_AD17      | 76         | S_AD7              | 147        | S_FRAME     | 179        | V <sub>CC</sub>    | 69         |

| GND             | 117        | P_AD18      | 74         | S_AD8              | 150        | S_GNT0      | 10         | $V_{CC}$           | 75         |

| GND             | 123        | P_AD19      | 73         | S_AD9              | 152        | S_GNT1      | 11         | V <sub>CC</sub>    | 81         |

| GND             | 136        | P_AD20      | 71         | S_AD10             | 154        | S_GNT2      | 13         | $V_{CC}$           | 91         |

| GND             | 142        | P_AD21      | 70         | S_AD11             | 159        | S_GNT3      | 14         | V <sub>CC</sub>    | 97         |

| GND             | 148        | P_AD22      | 68         | S_AD12             | 161        | S_GNT4      | 15         | $V_{CC}$           | 103        |

| GND             | 156        | P_AD23      | 67         | S_AD13             | 162        | S_GNT5      | 16         | V <sub>CC</sub>    | 105        |

| GND             | 158        | P_AD24      | 63         | S_AD14             | 164        | S_GNT6      | 17         | $V_{CC}$           | 108        |

| GND             | 160        | P_AD25      | 61         | S_AD15             | 165        | S_GNT7      | 18         | $V_{CC}$           | 114        |

| GND             | 166        | P_AD26      | 60         | S_AD16             | 182        | S_GNT8      | 19         | $V_{CC}$           | 120        |

| GND             | 174        | P_AD27      | 58         | S_AD17             | 183        | S_IRDY      | 177        | $V_{CC}$           | 131        |

| GND             | 181        | P_AD28      | 57         | S_AD18             | 185        | S_LOCK      | 172        | $V_{CC}$           | 139        |

| GND             | 187        | P_AD29      | 55         | S_AD19             | 186        | S_M66ENA    | 153        | $V_{CC}$           | 145        |

| GND             | 193        | P_AD30      |            | S_AD20             | 188        | S_PAR       | 168        | $V_{CC}$           | 151        |

| GND             | 199        | P_AD31      | 49         | S_AD21             | 189        | S_PERR      | 171        | V <sub>CC</sub>    | 202        |

| GND             | 205        | P_C/BE0     | 110        | S_AD22             | 191        | S_REQ0      | 207        | V <sub>CC</sub>    | 208        |

| GPIO0           | 28         | P_C/BE1     | 92         | S_AD23             | 192        | S_REQ1      | 2          | $V_{CC}$           | 157        |

| GPIO1           | 27         | P_C/BE2     | 79         | S_AD24             | 195        | S_REQ2      | 3          | $V_{CC}$           | 163        |

| GPIO2           | 25         | P_C/BE3     | 64         | S_AD25             | 197        | S_REQ3      | 4          | $V_{CC}$           | 170        |

| HS_ENUM         | 127        | P_CLK       | 45         | S_AD26             | 198        | S_REQ4      | 5          | V <sub>CC</sub>    | 178        |

| HS_LED          | 128        | P_DEVSEL    | 84         | S_AD27             | 200        | S_REQ5      | 6          | V <sub>CC</sub>    | 184        |

| HS_SWITCH/GPIO3 | 24         | P_FRAME     | 80         | S_AD28             | 201        | S_REQ6      | 7          | V <sub>CC</sub>    | 190        |

| MS0             | 155        | P_GNT       | 46         | S_AD29             | 203        | S_REQ7      | 8          | V <sub>CC</sub>    | 196        |

| MS1             | 106        | P_IDSEL     | 65         | S_AD30             | 204        | S_REQ8      | 9          |                    |            |

| MSK_IN          | 126        | P_IRDY      | 82         | S_AD31             | 206        | S_RST       | 22         |                    |            |

Table 2-5. 208-Terminal PPM Signal Names Sorted Alphabetically

| SIGNAL NAME     | PPM<br>NO. | SIGNAL NAME | PPM<br>NO. | SIGNAL NAME        | PPM<br>NO. | SIGNAL NAME | PPM<br>NO. | SIGNAL NAME        | PPM<br>NO. |

|-----------------|------------|-------------|------------|--------------------|------------|-------------|------------|--------------------|------------|

| BPCCE           | 44         | P_AD0       | 122        | P_LOCK             | 87         | S_C/BE0     | 149        | S_SERR             | 169        |

| CONFIG66        | 125        | P_AD1       | 121        | P_M66ENA           | 102        | S_C/BE1     | 167        | S_STOP             | 173        |

| GND             | 12         | P_AD2       | 119        | P_PAR              | 90         | S_C/BE2     | 180        | S_TRDY             | 176        |

| GND             | 20         | P_AD3       | 118        | P_PERR             | 88         | S_C/BE3     | 194        | S_V <sub>CCP</sub> | 135        |

| GND             | 31         | P_AD4       | 116        | P_REQ              | 47         | S_CFN       | 23         | TCK                | 133        |

| GND             | 37         | P_AD5       | 115        | P_RST              | 43         | S_CLK       | 21         | TDI                | 129        |

| GND             | 48         | P_AD6       | 113        | P_SERR             | 89         | S_CLKOUT0   | 29         | TDO                | 130        |

| GND             | 52         | P_AD7       | 112        | P_STOP             | 85         | S_CLKOUT1   | 30         | TMS                | 132        |

| GND             | 54         | P_AD8       | 109        | P_TRDY             | 83         | S_CLKOUT2   | 32         | TRST               | 134        |

| GND             | 59         | P_AD9       | 107        | P_V <sub>CCP</sub> | 124        | S_CLKOUT3   | 33         | V <sub>CC</sub>    | 1          |

| GND             | 66         | P_AD10      | 101        | S_AD0              | 137        | S_CLKOUT4   | 35         | V <sub>CC</sub>    | 26         |

| GND             | 72         | P_AD11      | 99         | S_AD1              | 138        | S_CLKOUT5   | 36         | $V_{CC}$           | 34         |

| GND             | 78         | P_AD12      | 98         | S_AD2              | 140        | S_CLKOUT6   | 38         | $V_{CC}$           | 40         |

| GND             | 86         | P_AD13      | 96         | S_AD3              | 141        | S_CLKOUT7   | 39         | V <sub>CC</sub>    | 51         |

| GND             | 94         | P_AD14      | 95         | S_AD4              | 143        | S_CLKOUT8   | 41         | V <sub>CC</sub>    | 53         |

| GND             | 100        | P_AD15      | 93         | S_AD5              | 144        | S_CLKOUT9   | 42         | $V_{CC}$           | 56         |

| GND             | 104        | P_AD16      | 77         | S_AD6              | 146        | S_DEVSEL    | 175        | $V_{CC}$           | 62         |

| GND             | 111        | P_AD17      | 76         | S_AD7              | 147        | S_FRAME     | 179        | V <sub>CC</sub>    | 69         |

| GND             | 117        | P_AD18      | 74         | S_AD8              | 150        | S_GNT0      | 10         | V <sub>CC</sub>    | 75         |

| GND             | 123        | P_AD19      | 73         | S_AD9              | 152        | S_GNT1      | 11         | V <sub>CC</sub>    | 81         |

| GND             | 136        | P_AD20      | 71         | S_AD10             | 154        | S_GNT2      | 13         | V <sub>CC</sub>    | 91         |

| GND             | 142        | P_AD21      | 70         | S_AD11             | 159        | S_GNT3      | 14         | V <sub>CC</sub>    | 97         |

| GND             | 148        | P_AD22      | 68         | S_AD12             | 161        | S_GNT4      | 15         | V <sub>CC</sub>    | 103        |

| GND             | 156        | P_AD23      | 67         | S_AD13             | 162        | S_GNT5      | 16         | V <sub>CC</sub>    | 105        |

| GND             | 158        | P_AD24      | 63         | S_AD14             | 164        | S_GNT6      | 17         | V <sub>CC</sub>    | 108        |

| GND             | 160        | P_AD25      | 61         | S_AD15             | 165        | S_GNT7      | 18         | $V_{CC}$           | 114        |

| GND             | 166        | P_AD26      | 60         | S_AD16             | 182        | S_GNT8      | 19         | $V_{CC}$           | 120        |

| GND             | 174        | P_AD27      | 58         | S_AD17             | 183        | S_IRDY      | 177        | V <sub>CC</sub>    | 131        |

| GND             | 181        | P_AD28      | 57         | S_AD18             | 185        | S_LOCK      | 172        | V <sub>CC</sub>    | 139        |

| GND             | 187        | P_AD29      | 55         | S_AD19             | 186        | S_M66ENA    | 153        | $V_{CC}$           | 145        |

| GND             | 193        | P_AD30      | 50         | S_AD20             | 188        | S_PAR       | 168        | $V_{CC}$           | 151        |

| GND             | 199        | P_AD31      | 49         | S_AD21             | 189        | S_PERR      | 171        | V <sub>CC</sub>    | 202        |

| GND             | 205        | P_C/BE0     | 110        | S_AD22             | 191        | S_REQ0      | 207        | V <sub>CC</sub>    | 208        |

| GPIO0           | 28         | P_C/BE1     | 92         | S_AD23             | 192        | S_REQ1      | 2          | V <sub>CC</sub>    | 157        |

| GPIO1           | 27         | P_C/BE2     | 79         | S_AD24             | 195        | S_REQ2      | 3          | $V_{CC}$           | 163        |

| GPIO2           | 25         | P_C/BE3     | 64         | S_AD25             | 197        | S_REQ3      | 4          | V <sub>CC</sub>    | 170        |

| HS_ENUM         | 127        | P_CLK       | 45         | S_AD26             | 198        | S_REQ4      | 5          | V <sub>CC</sub>    | 178        |

| HS_LED          | 128        | P_DEVSEL    | 84         | S_AD27             | 200        | S_REQ5      | 6          | V <sub>CC</sub>    | 184        |

| HS_SWITCH/GPIO3 | 24         | P_FRAME     | 80         | S_AD28             | 201        | S_REQ6      | 7          | V <sub>CC</sub>    | 190        |

| MS0             | 155        | P_GNT       | 46         | S_AD29             | 203        | S_REQ7      | 8          | V <sub>CC</sub>    | 196        |

| MS1             | 106        | P_IDSEL     | 65         | S_AD30             | 204        | S_REQ8      | 9          |                    |            |

| MSK_IN          | 126        | P_IRDY      | 82         | S_AD31             | 206        | S_RST       | 22         |                    |            |

Table 2-6. 257-Terminal GHK/ZHK Signal Names Sorted Alphabetically

|                 |            |             |            | TIN/ZITIN Signal |            |                    |            | ,           |            |

|-----------------|------------|-------------|------------|------------------|------------|--------------------|------------|-------------|------------|

| SIGNAL NAME     | GHK<br>NO. | SIGNAL NAME | GHK<br>NO. | SIGNAL NAME      | GHK<br>NO. | SIGNAL NAME        | GHK<br>NO. | SIGNAL NAME | GHK<br>NO. |

| BPCCE           | N5         | NC          | A18        | NC               | V19        | P_FRAME            | W11        | S_AD29      | B5         |

| CONFIG66        | L18        | NC          | B1         | NC               | W2         | P_GNT              | R1         | S_AD30      | E6         |

| GND             | A7         | NC          | B2         | NC               | W3         | P_IDSEL            | W7         | S_AD31      | A4         |

| GND             | A12        | NC          | ВЗ         | NC               | W17        | P_IRDY             | U11        | S_CFN       | J6         |

| GND             | A14        | NC          | B9         | NC               | W18        | P_LOCK             | P12        | S_CLK       | J3         |

| GND             | B10        | NC          | B16        | P_AD0            | M18        | P_M66ENA           | W16        | S_CLKOUT0   | L1         |

| GND             | C5         | NC          | B17        | P_AD1            | M17        | P_PAR              | V13        | S_CLKOUT1   | L2         |

| GND             | C15        | NC          | B18        | P_AD2            | N19        | P_PERR             | R12        | S_CLKOUT2   | L5         |

| GND             | D19        | NC          | B19        | P_AD3            | N18        | P_REQ              | P6         | S_CLKOUT3   | M1         |

| GND             | E7         | NC          | C1         | P_AD4            | M14        | P_RST              | P2         | S_CLKOUT4   | МЗ         |

| GND             | E9         | NC          | C2         | P_AD5            | P19        | P_SERR             | W13        | S_CLKOUT5   | M6         |

| GND             | F13        | NC          | СЗ         | P_AD6            | P18        | P_STOP             | W12        | S_CLKOUT6   | N1         |

| GND             | F18        | NC          | C4         | P_AD7            | P17        | P_TRDY             | P11        | S_CLKOUT7   | N2         |

| GND             | G3         | NC          | C10        | P_AD8            | N14        | P_V <sub>CCP</sub> | L19        | S_CLKOUT8   | N6         |

| GND             | H15        | NC          | C16        | P_AD9            | R17        | S_AD0              | J15        | S_CLKOUT9   | P1         |

| GND             | J2         | NC          | C17        | P_AD10           | U15        | S_AD1              | H19        | S_C/BE0     | G15        |

| GND             | J14        | NC          | C18        | P_AD11           | V15        | S_AD2              | H17        | S_C/BE1     | F12        |

| GND             | L6         | NC          | C19        | P_AD12           | P14        | S_AD3              | H14        | S_C/BE2     | A10        |

| GND             | M5         | NC          | D1         | P_AD13           | U14        | S_AD4              | G19        | S_C/BE3     | В7         |

| GND             | M19        | NC          | D3         | P_AD14           | R13        | S_AD5              | G18        | S_DEVSEL    | A11        |

| GND             | N17        | NC          | D17        | P_AD15           | W14        | S_AD6              | G14        | S_FRAME     | F11        |

| GND             | P5         | NC          | D18        | P_AD16           | U10        | S_AD7              | F19        | S_GNT0      | F1         |

| GND             | R8         | NC          | E5         | P_AD17           | V10        | S_AD8              | F17        | S_GNT1      | H6         |

| GND             | R10        | NC          | K19        | P_AD18           | P9         | S_AD9              | F14        | S_GNT2      | G2         |

| GND             | R14        | NC          | L3         | P_AD19           | R9         | S_AD10             | F15        | S_GNT3      | G1         |

| GND             | R19        | NC          | R2         | P_AD20           | V9         | S_AD11             | E14        | S_GNT4      | H5         |

| GND             | U1         | NC          | T3         | P_AD21           | W9         | S_AD12             | B15        | S_GNT5      | НЗ         |

| GND             | U5         | NC          | T17        | P AD22           | V8         | S AD13             | A15        | S_GNT6      | H2         |

| GND             | U9         | NC          | U2         | P_AD23           | U8         | S_AD14             | B14        | S_GNT7      | H1         |

| GND             | U12        | NC          | U3         | P AD24           | U7         | S_AD15             | E13        | S_GNT8      | J1         |

| GND             | V6         | NC          | U4         | P_AD25           | W6         | S_AD16             | E10        | S IRDY      | C11        |

| GND             | V14        | NC          | U16        | P_AD26           | R7         | S_AD17             | F10        | S_LOCK      | C12        |

| GPIO0           | K6         | NC          | U17        | P_AD27           | U6         | S_AD18             | C9         | S_M66ENA    | E18        |

| GPIO1           | K5         | NC          | U18        | P_AD28           | W5         | S_AD19             | F9         | S_PAR       | C13        |

| GPIO2           | K2         | NC          | U19        | P_AD29           | R6         | S_AD20             | A8         | S_PERR      | E12        |

| HS_ENUM         | L15        | NC          | V1         | P AD30           | T1         | S AD21             | В8         | S REQ0      | B4         |

| HS_LED          | L14        | NC          | V2         | P_AD31           | R3         | S_AD22             | F8         | S_REQ1      | E3         |

| HS_SWITCH/GPIO3 | K1         | NC          | V3         | P_CLK            | P3         | S_AD23             | E8         | S_REQ2      | F5         |

| MSK_IN          | L17        | NC          | V4         | P_C/BE0          | R18        | <br>S_AD24         | C7         | S_REQ3      | G6         |

| MS0             | E17        | NC          | V5         | P_C/BE1          | P13        | <br>S_AD25         | A6         | S_REQ4      | E2         |

| MS1             | T19        | NC          | V12        | P_C/BE2          | P10        | <br>S_AD26         | B6         | S_REQ5      | E1         |

| NC              | A2         | NC          | V17        | P_C/BE3          | V7         | <br>S_AD27         | C6         | S_REQ6      | F3         |

| NC              | A17        | NC          | V18        | P_DEVSEL         | R11        | S_AD28             | A5         | S_REQ7      | F2         |

Table 2-6. 257-Terminal GHK/ZHK Signal Names Sorted Alphabetically (Continued)

| SIGNAL NAME        | GHK<br>NO. | SIGNAL NAME     | GHK<br>NO. | SIGNAL NAME     | GHK<br>NO. | SIGNAL NAME     | GHK<br>NO. | SIGNAL NAME     | GHK<br>NO. |

|--------------------|------------|-----------------|------------|-----------------|------------|-----------------|------------|-----------------|------------|

| S_REQ8             | G5         | TMS             | K14        | V <sub>CC</sub> | E11        | $V_{CC}$        | M2         | $V_{CC}$        | V11        |

| S_RST              | J5         | TRST            | J18        | V <sub>CC</sub> | E19        | V <sub>CC</sub> | N3         | $V_{CC}$        | V16        |

| S_SERR             | B13        | V <sub>CC</sub> | А3         | V <sub>CC</sub> | F6         | $V_{CC}$        | N15        | $V_{CC}$        | W4         |

| S_STOP             | B12        | V <sub>CC</sub> | A9         | V <sub>CC</sub> | F7         | V <sub>CC</sub> | P7         | V <sub>CC</sub> | W8         |

| S_TRDY             | B11        | V <sub>CC</sub> | A13        | V <sub>CC</sub> | M15        | V <sub>CC</sub> | P8         | V <sub>CC</sub> | W10        |

| S_V <sub>CCP</sub> | J17        | V <sub>CC</sub> | A16        | V <sub>CC</sub> | G17        | V <sub>CC</sub> | P15        | V <sub>CC</sub> | W15        |

| TCK                | J19        | V <sub>CC</sub> | C8         | V <sub>CC</sub> | H18        | $V_{CC}$        | T2         |                 |            |

| TDI                | K18        | V <sub>CC</sub> | C14        | V <sub>CC</sub> | K3         | $V_{CC}$        | T18        |                 |            |

| TDO                | K17        | V <sub>CC</sub> | D2         | $V_{CC}$        | K15        | $V_{CC}$        | U13        |                 |            |

The terminals are grouped in tables by functionality, such as PCI system function and power-supply function (see Table 2–7 through Table 2–15). The terminal numbers also are listed for convenient reference.

Table 2-7. Primary PCI System Terminals

| TE    | RMINAL             |                    |     |                                                                                                                                                                                                                                                                                                                                                                                            |

|-------|--------------------|--------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME  | PDV/<br>PPM<br>NO. | GHK/<br>ZHK<br>NO. | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                |

| P_CLK | 45                 | P3                 | I   | Primary PCI bus clock. P_CLK provides timing for all transactions on the primary PCI bus. All primary PCI signals are sampled at rising edge of P_CLK.                                                                                                                                                                                                                                     |

| P_RST | 43                 | P2                 | I   | PCI reset. When the primary PCI bus reset is asserted, $\overline{P\_RST}$ causes the bridge to put all output buffers in a high-impedance state and reset all internal registers. When asserted, the device is completely nonfunctional. During $\overline{P\_RST}$ , the secondary interface is driven low. After $\overline{P\_RST}$ is deasserted, the bridge is in its default state. |

Table 2-8. Primary PCI Address and Data Terminals

| TERI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | MINAL                                                                                                                                                                                                   |                                                                                                               |     | ne 2-6. Filliary PCI Address and Data Terminals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | PDV/<br>PPM<br>NO.                                                                                                                                                                                      | GHK/<br>ZHK<br>NO.                                                                                            | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| P_AD31 P_AD30 P_AD29 P_AD28 P_AD26 P_AD25 P_AD24 P_AD23 P_AD22 P_AD21 P_AD20 P_AD19 P_AD18 P_AD15 P_AD16 P_AD15 P_AD14 P_AD13 P_AD12 P_AD11 P_AD10 P_AD2 P_AD11 P_AD10 P_AD2 P_AD11 P_AD3 P_AD6 P_AD5 P_AD6 P_AD5 P_AD6 P_AD7 P_AD6 P_AD7 P_AD6 P_AD7 P_AD6 P_AD7 P_AD7 P_AD6 P_AD7 P_AD7 P_AD7 P_AD8 P_AD7 P_AD8 P_AD7 P_AD8 P_AD7 P_AD9 P_AD9 P_AD9 P_AD9 P_AD9 P_AD9 P_AD9 P_AD9 P_AD1 P_AD1 | 49<br>50<br>55<br>57<br>58<br>60<br>61<br>63<br>67<br>68<br>70<br>71<br>73<br>74<br>76<br>77<br>93<br>95<br>96<br>98<br>99<br>101<br>107<br>109<br>112<br>113<br>115<br>116<br>118<br>119<br>121<br>122 | R3 T1 R6 W5 U6 R7 W6 U7 U8 V8 W9 V9 R9 P9 V10 U10 W14 R13 U14 P14 V15 R17 N14 P17 P18 P19 M14 N18 N19 M17 M18 | I/O | Primary address/data bus. These signals make up the multiplexed PCI address and data bus on the primary interface. During the address phase of a primary bus PCI cycle, P_AD31-P_AD0 contain a 32-bit address or other destination information. During the data phase, P_AD31-P_AD0 contain data.                                                                                                                                                                                                                                       |  |  |  |

| P_C/BE3<br>P_C/BE2<br>P_C/BE1<br>P_C/BE0                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 64<br>79<br>92<br>110                                                                                                                                                                                   | V7<br>P10<br>P13<br>R18                                                                                       | I/O | Primary bus commands and byte enables. These signals are multiplexed on the same PCI terminals. During the address phase of a primary bus PCI cycle, P_C/BE3-P_C/BE0 define the bus command. During the data phase, this 4-bit bus is used as byte enables. The byte enables determine which byte paths of the full 32-bit data bus carry meaningful data. P_C/BE0 applies to byte 0 (P_AD7-P_AD0), P_C/BE1 applies to byte 1 (P_AD15-P_AD8), P_C/BE2 applies to byte 2 (P_AD23-P_AD16), and P_C/BE3 applies to byte 3 (P_AD31-P_AD24). |  |  |  |

Table 2-9. Primary PCI Interface Control Terminals

| TERI     | MINAL              |                    |     | bie 2-9. Frimary FCI interface Control Terminals                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|----------|--------------------|--------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME     | PDV/<br>PPM<br>NO. | GHK/<br>ZHK<br>NO. | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| P_DEVSEL | 84                 | R11                | I/O | Primary device select. The bridge asserts <u>P_DEVSEL</u> to claim a PCI cycle as the target device. As a PCI master on the primary bus, the bridge monitors <u>P_DEVSEL</u> until a target responds. If no target responds before time-out occurs, then the bridge terminates the cycle with a master abort.                                                                                                                                                                                 |  |

| P_FRAME  | 80                 | W11                | I/O | Primary cycle frame. P_FRAME is driven by the master of a primary bus cycle. P_FRAME is asserted to indicate that a bus transaction is beginning, and data transfers continue while this signal is asserted. When P_FRAME is deasserted, the primary bus transaction is in the final data phase.                                                                                                                                                                                              |  |

| P_GNT    | 46                 | R1                 | _   | Primary bus grant to bridge. P_GNT is driven by the primary PCI bus arbiter to grant the bridge access to the primary PCI bus after the current data transaction has completed. P_GNT may or may not follow a primary bus request, depending on the primary bus arbitration algorithm.                                                                                                                                                                                                        |  |