# 66AK2H06/12/14 Multicore DSP+ARM KeyStone II SOC Silicon Revisions 1.0, 1.1, 2.0, 3.0, 3.1

# Silicon Errata

Literature Number: SPRZ402E June 2013–Revised June 2017

# **Contents**

| 1     | Device and Development Support Tool Nomenclature  | 4  |

|-------|---------------------------------------------------|----|

| 2     | Package Symbolization and Revision Identification | 5  |

| 3     | ARM-Specific Information                          | 7  |

| 4     | Silicon Updates                                   | 7  |

| Revis | sion History                                      | 86 |

#### www.ti.com

# **List of Figures**

| 1  | Lot Trace Code Example for 66AK2H06/12/14 (AWW Package)                       | . 5 |

|----|-------------------------------------------------------------------------------|-----|

| 2  | SRIO SerDes in Loopback Mode                                                  | 20  |

| 3  | Software Reset Using the RSTCTRL Register                                     | 30  |

| 4  | Reset Source Code                                                             | 31  |

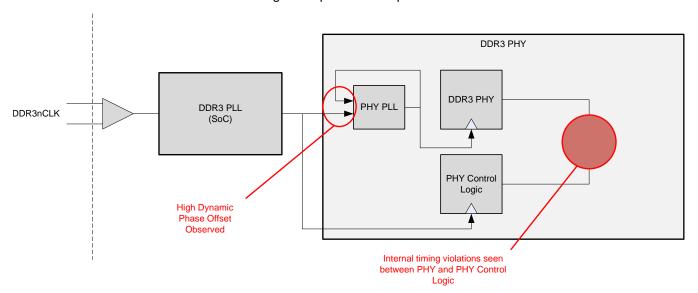

| 5  | DDR3 PHY                                                                      | 43  |

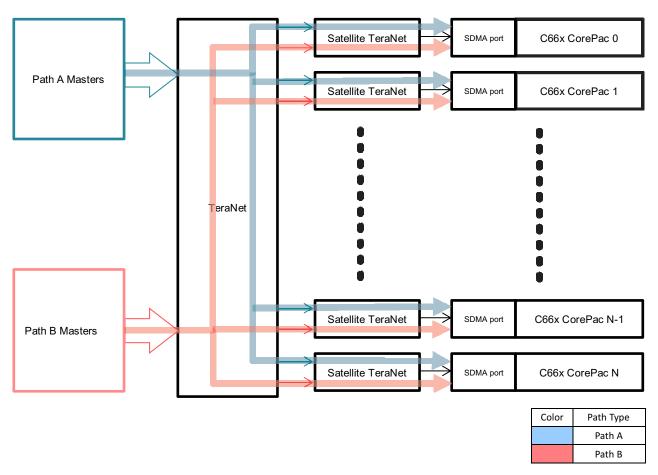

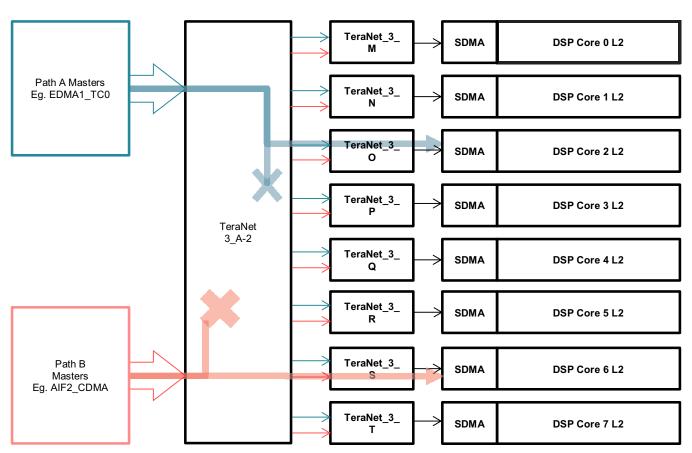

| 6  | Satellite TeraNet Paths                                                       | 46  |

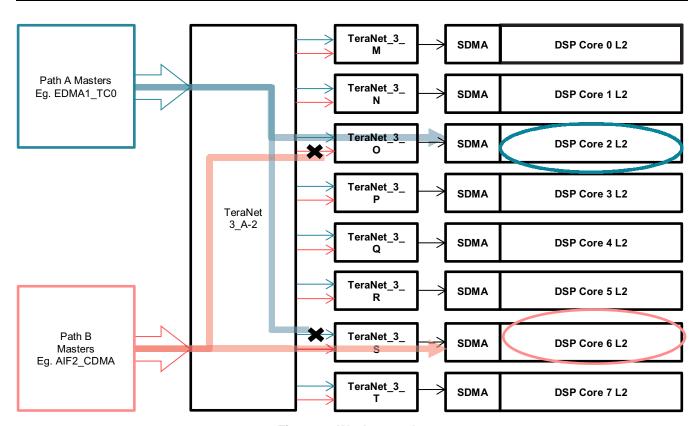

| 7  | Hang Scenario                                                                 | 47  |

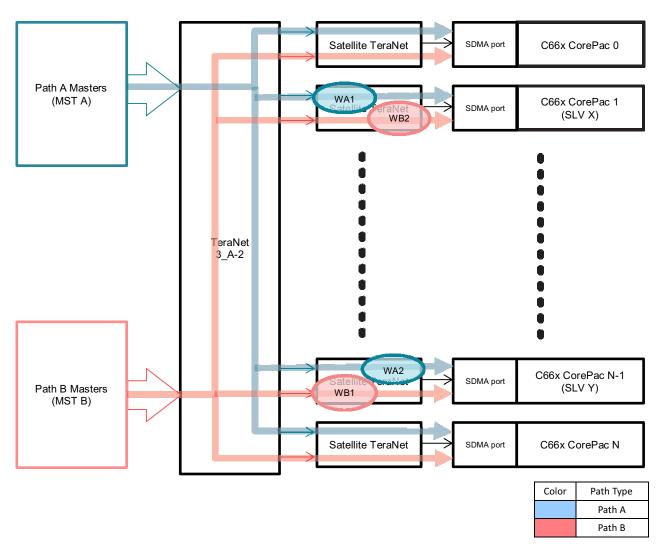

| 8  | Workaround 1                                                                  | 49  |

| 9  | Workaround 2                                                                  | 50  |

| 10 | RX Path Block Diagram                                                         | 84  |

|    |                                                                               |     |

|    | List of Tables                                                                |     |

| 1  | Lot Trace Codes                                                               | . 5 |

| 2  | Silicon Revision Variables                                                    | . 6 |

| 3  | Cortex-A15 Processor Version and REVIDR                                       | . 7 |

| 4  | Silicon Revision 1.0, 1.1, 2.0, 3.0, and 3.1 Updates                          | . 7 |

| 5  | DDR3A                                                                         | 19  |

| 6  | DDR3B                                                                         | 19  |

| 7  | Impact on Various Lane Speeds                                                 | 23  |

| 8  | Master Behavior in Response to sstatus/rstatus Flagged Due to DDR3 ECC Errors | 27  |

| 9  | DDR3-1600                                                                     | 43  |

| 10 | DDR3-1333                                                                     | 44  |

| 11 | DDR3-1066                                                                     | 44  |

| 12 | DDR3-800                                                                      | 45  |

| 13 | SerDes peripherals impacted by RX Boost equalization problem                  | 84  |

# 66AK2H06/12/14 Multicore DSP+ARM KeyStone II SOC Silicon Revisions 1.0, 1.1, 2.0, 3.0, 3.1

This document describes the silicon updates to the functional specifications for the 66AK2H06/12/14 fixed-/floating-point digital signal processor. See the device-specific data manual for more information.

#### 1 Device and Development Support Tool Nomenclature

To designate the stages in the product development cycle, TI assigns prefixes to the part numbers of all devices and support tools. Each family member has one of two prefixes: X or [blank]. These prefixes represent evolutionary stages of product development from engineering prototypes through fully qualified production devices/tools.

Device development evolutionary flow:

- X: Experimental device that is not necessarily representative of the final device's electrical specifications

- [Blank]: Fully qualified production device

Support tool development evolutionary flow:

- X: Development-support product that has not yet completed Texas Instruments internal qualification testing.

- [Blank]: Fully qualified development-support product

Experimental (X) and fully qualified [Blank] devices and development-support tools are shipped with the following disclaimer:

#### • Developmental product is intended for internal evaluation purposes.

Fully qualified and production devices and development-support tools have been characterized fully, and the quality and reliability of the device have been demonstrated fully. Tl's standard warranty applies.

Predictions show that experimental devices (X) have a greater failure rate than the standard production devices. Texas Instruments recommends that these devices not be used in any production system because their expected end-use failure rate still is undefined. Only qualified production devices are to be used.

TI device nomenclature also includes a suffix with the device family name. This suffix indicates the package type (for example, AAW), the temperature range (for example, blank is the default case temperature range), and the device speed range, in Megahertz (for example, blank is 1000 MHz [1 GHz]).

For device part numbers and further ordering information for 66AK2H06/12/14 in the AWW package type, see the TI website www.ti.com or contact your TI sales representative.

# 2 Package Symbolization and Revision Identification

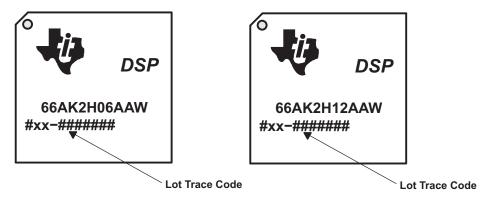

The device revision can be determined by the lot trace code marked on the top of the package. The location of the lot trace code for the AWW package is shown in Figure 1. The figure also shows an example of 66AK2H06/12/14 package symbolization.

Figure 1. Lot Trace Code Example for 66AK2H06/12/14 (AWW Package)

Silicon revision correlates to the lot trace code marked on the package. This code is of the format #xx-#######. Note that there may be an additional leading character (not shown in this example) and xx may actually be two or three characters. If xx is **10**, then the silicon is revision 1.0. Table 1 lists the silicon revisions associated with each lot trace code for the 66AK2H06/12/14 devices.

| Lot Trace Code (xx) | Silicon Revision | Comments                 |

|---------------------|------------------|--------------------------|

| 10                  | 1.0              | Initial silicon revision |

| 11                  | 1.1              | Silicon revision 1.1     |

| 20                  | 2.0              | Silicon revision 2.0     |

| 30                  | 3.0              | Silicon revision 3.0     |

| 31                  | 3.1              | Silicon revision 3.1     |

**Table 1. Lot Trace Codes**

The 66AK2H06/12/14 device contains multiple read-only register fields that report revision values. The JTAG ID (JTAGID) and C66x CorePac Revision ID registers allow the customer to read the current device and CPU level revision of the 66AK2H06/12/14.

The JTAG ID register (JTAGID) is a read-only register that identifies to the customer the JTAG/Device ID.

The C66x CorePac Revision ID register is a read-only register that identifies to the customer the revision of the C66x CorePac. The value in the VERSION field of the C66x CorePac Revision ID Register changes based on the version of the C66x CorePac implemented on the device. More details on the C66x CorePac Revision ID register can be found in the part-specific data manual.

Table 2 shows the contents of the C66x CorePac REVID Register, and the JTAGID register for each silicon revision of the 66AK2H06/12/14 device.

#### **Table 2. Silicon Revision Variables**

| Silicon Revision | C66x CorePac REVID Register (address location: 0x0181_2000) | 66AK2H06/12/14 JTAGID Register (address location: 0x0262_0018) |

|------------------|-------------------------------------------------------------|----------------------------------------------------------------|

| 1.0              | 0x0009_0000                                                 | 0x0b98_102f                                                    |

| 1.1              | 0x0009_0002                                                 | 0x1b98_102f                                                    |

| 2.0              | 0x0009_0003                                                 | 0x2b98_102f                                                    |

| 3.0              | 0x0009_0003                                                 | 0x3b98_102f                                                    |

| 3.1              | 0x0009_0003                                                 | 0xbb98_102f                                                    |

More details on the JTAG ID and CorePac Revision ID Registers can be found in the device-specific data manual.

#### 3 ARM-Specific Information

This document does not list the errata for Cortex<sup>™</sup>-A15 MPCore. For the latest information regard ARM issues, please see the following ARM web pages:

For the latest information regarding ARM issues that may not be addressed in this errata document, see the following ARM Web pages:

- http://infocenter.arm.com/help/index.jsp

- http://infocenter.arm.com/help/index.jsp?topic=/com.arm.doc.set.cortexa/index.html

Table 3 provides the ARM Cortex-A15 MPCore processor version and REVIDR used by the 66AK2H06/12/14.

| SoC           | A15 Version | ARM REVIDR                |

|---------------|-------------|---------------------------|

| 66AK2Hx PG1.1 | r2p4        | 0x0002 (Bit 1 = 1)        |

| 66AK2Hx PG2.0 | r2p4        | 0x020A (Bits 1, 3, 9 = 1) |

| 66AK2Hx PG3.0 | r2p4        | 0x020A (Bits 1, 3, 9 = 1) |

| 66AK2Hx PG3.1 | r2p4        | 0x020A (Bits 1, 3, 9 = 1) |

Table 3. Cortex-A15 Processor Version and REVIDR

The ARM product revision  $r_mp_n$  indicates the major and minor revision status of the ARM core incorporated in this device. Additionally, for a specific product revision a few additional erratum may be fixed, which can be determined by reading the ARM REVIDR register where a set bit indicates that the erratum is fixed in this ARM revision. A combination of this information can be used when referring to the *ARM Processor Cortex*<sup>TM</sup>-A15 MPCore – Product Errata Notice documentation to infer the erratum applicability to this device.

The definition of the Revision ID Register can be found at the following location:

http://infocenter.arm.com/help/index.jsp?topic=/com.arm.doc.ddi0438i/CIHEJBDJ.html

#### 4 Silicon Updates

lists the silicon updates applicable to each silicon revision. For details on each advisory, click on the link below.

| Table 4. Silicon Revision 1.0, | 1.1, 2.0, 3.0, and 3.1 Updates |

|--------------------------------|--------------------------------|

|           |                                                                       |             | Applies To Silicon Revision |     |     |     |     |  |

|-----------|-----------------------------------------------------------------------|-------------|-----------------------------|-----|-----|-----|-----|--|

| Category  | Silicon Update Advisory                                               | See         | 1.0                         | 1.1 | 2.0 | 3.0 | 3.1 |  |

| ROM       | Boot ROM Missed EMIF PHY Configuration Registers                      | Advisory 1  | Х                           |     |     |     |     |  |

| NOR XIP   | Execution in Parallel (XIP) from NOR Flash on ARM Does Not Work       | Advisory 2  | Х                           | Х   | Х   | Х   | Х   |  |

| Boot      | ARM L2 Latency is Not Set Correctly                                   | Advisory 3  | Х                           |     |     |     |     |  |

| SRIO      | SRIO Boot Mode Packet DMA Cleanup<br>Missing                          | Advisory 4  | Х                           |     |     |     |     |  |

| Sync-E    | Sync-Ethernet Push Event IO Control Tie-<br>Off Incorrect             | Advisory 5  | Х                           |     |     |     |     |  |

| ROM       | EMIF Boot (NOR flash) Mode Not Working<br>When ARM Master Boot        | Advisory 8  | Х                           |     |     |     |     |  |

| ARM       | 1.4-Ghz ARM is Not Supported                                          | Advisory 9  | Х                           |     |     |     |     |  |

| DDR3      | DDR3A Lanes 5 and DDR3B Lane 8 Have PHY to PUB DFI Hold Time Failures | Advisory 10 | Х                           |     |     |     |     |  |

| SRIO      | Corruption of Control Characters In SRIO<br>Line Loopback Mode        | Advisory 13 | Х                           | Х   | Х   | Х   | Х   |  |

| Hyperlink | HyperLink Temporary Blocking                                          | Advisory 14 | Х                           | Х   | Х   | Х   | Х   |  |

| Reset     | RESETSTAT Signal Driven High                                          | Advisory 15 | Х                           | Х   | Х   | Х   | Х   |  |

Table 4. Silicon Revision 1.0, 1.1, 2.0, 3.0, and 3.1 Updates (continued)

|           |                                                                                                                         |              | Applies To Silicon Revision |     |     |     |     |  |

|-----------|-------------------------------------------------------------------------------------------------------------------------|--------------|-----------------------------|-----|-----|-----|-----|--|

| Category  | Silicon Update Advisory                                                                                                 | See          | 1.0                         | 1.1 | 2.0 | 3.0 | 3.1 |  |

| SRIO      | SRIO Control Symbols Are Sent More Often Than Required                                                                  | Advisory 16  | Х                           | Х   | Х   | Х   | Х   |  |

| ccs       | System Reset Operation Disconnects SoC from CCS                                                                         | Advisory 17  | Х                           | Х   | Х   | Х   | Х   |  |

| ARM       | ARM CorePac Power Down and<br>Hibernation Modes Not Supported                                                           | Advisory 19  | Х                           | Х   |     |     |     |  |

| DDR3      | False DDR3 Write ECC Error Reported Under Certain Conditions                                                            | Advisory 20  | Х                           | Х   | Х   | Х   | Х   |  |

| DDR3      | DDR3 Leveling Issue                                                                                                     | Advisory 21  | Х                           | Х   |     |     |     |  |

| PCle      | PCIE MSI/Legacy IRQ Does Not Work for Root Complex                                                                      | Advisory 22  | Х                           | Х   | Х   | Х   | Х   |  |

| DDR3      | SES Port Should Only be Used for DDR3A Accesses                                                                         | Advisory 23  | Х                           | Х   |     |     |     |  |

| PCle      | Descriptors Placed in PCIe Memory Space can Cause Problems                                                              | Advisory 28  | Х                           | Х   | Х   | Х   | Х   |  |

| 10GbE     | 10GbE PCS Causes Data Corruption                                                                                        | Advisory 29  | Х                           | Х   | Х   | Х   | Х   |  |

| 10GbE     | 10GbE PCB Channel Loss Limited to 20 dB                                                                                 | Advisory 30  | Х                           | Х   | Х   | Х   | Х   |  |

| HyperLink | HyperLink Channel Loss                                                                                                  | Advisory 31  | Х                           | Х   | Х   | Х   | Х   |  |

| HyperLink | HyperLink Data Rate Limited to 40Gbaud Issue                                                                            | Advisory 33  | Х                           | Х   | Х   | Х   | Х   |  |

| DDR3      | DDR3 Limited to Highest Data Rates Due to<br>Possibility of PLL Instability During<br>Temperature Changes After Startup | Advisory 34  | Х                           | Х   | Х   |     |     |  |

| DDR3      | Restrictions on DDR3 PLL Configuration And DDR3nCLK to Eliminate DDR3 Errors Due to PLL Dynamic Phase Offset            | Advisory 35  | Х                           | Х   | Х   |     |     |  |

| TeraNet   | Two Masters Accessing Two C66x CorePac<br>L2 Memories Can Cause TeraNet Hang                                            | Advisory 36  | Х                           | Х   | Х   |     |     |  |

| USB       | USB3.0 PHY Does Not Meet USB<br>Specification: Rev 3.0 RX Jitter Tolerance<br>Mask                                      | Advisory 37  | Х                           | Х   | Х   | Х   | Х   |  |

| PCI       | PCI-Express Hot Reset Not Handled During Boot                                                                           | Advisory 38  | Х                           | Х   | Х   |     |     |  |

| CPSW      | CPSW Stall if Duplex Changes During Transmission                                                                        | Advisory 39  | Х                           | Х   | Х   | Х   | Х   |  |

| ROM       | NAND Boot Failure When Booting Single<br>Block Backup Images                                                            | Advisory 40  | Х                           | Х   | Х   |     |     |  |

| ROM       | NAND Boot Failure With Bit Errors in ECC                                                                                | Advisory 41  | X                           | Х   | Х   |     |     |  |

| ROM       | ARM Ethernet Boot Reinitializes the Switch With Reset Isolation Enabled, Which May Cause Lockup                         | Advisory 42  | X                           | Х   | X   |     |     |  |

| SerDes    | SerDes RX Adapts to a BOOST Value of 0 and Cannot Move From a Value of 0                                                | Advisory 44  | Х                           | Х   | Х   | Х   | Х   |  |

| PCle      | PCIe link power states other than L0 are not supported on some Keystone II SOCs                                         | Advisory 45  | Х                           | Х   | Х   | Х   | Х   |  |

| QMSS      | Queue Diversion Failure                                                                                                 | Advisory 46  | Х                           | X   | Х   |     |     |  |

| ROM       | SGMII, SRIO, Hyperlink, and PCIe boot may fail on some devices                                                          | Advisory 47  | Х                           | Х   | Х   | Х   |     |  |

| SPI       | SPI Boot Size Limitation, C66x Master Boot                                                                              | Usage Note 1 | Х                           |     |     |     |     |  |

| ARM       | ARM Core Hangs if Timer is Accessed<br>While ARM Core is in Wait-In-Reset State                                         | Usage Note 2 | Х                           | Х   |     |     |     |  |

| Debug     | Debug System (DebugSS) Trace Buffer (TBR) EDMA via System Port is not Functional                                        | Usage Note 3 | Х                           | Х   |     |     |     |  |

| Boot      | ARM Boot Can Fail When Interrupt Enabled                                                                                | Usage Note 4 | Х                           | Х   |     |     |     |  |

# Table 4. Silicon Revision 1.0, 1.1, 2.0, 3.0, and 3.1 Updates (continued)

|                  |                                                                                         |               | Ap  | plies T | o Silico | n Revis | ion |

|------------------|-----------------------------------------------------------------------------------------|---------------|-----|---------|----------|---------|-----|

| Category         | Silicon Update Advisory                                                                 | See           | 1.0 | 1.1     | 2.0      | 3.0     | 3.1 |

| Boot             | Boot I <sup>2</sup> C Frequency Incorrect                                               | Usage Note 5  | Х   | Х       | Х        | Х       | Х   |

| DDR3             | Access to DDR3 Without Configuring PHY Properly Can Cause Hang                          | Usage Note 6  | Х   | Х       | Х        | Х       | Х   |

| Power            | C66x CorePac and ARM CorePac AVS<br>Rails                                               | Usage Note 7  | Х   | Х       | Х        | Х       | Х   |

| Power            | Core Wake Up on RESET                                                                   | Usage Note 9  | Х   | Х       | Х        | Х       | Х   |

| I <sup>2</sup> C | I <sup>2</sup> C Bus Hang After Master Reset                                            | Usage Note 10 | Х   | Х       | Х        | Х       | Х   |

| PLL              | Minimizing Main PLL Jitter                                                              | Usage Note 11 | Х   | Х       | Х        | Х       | Х   |

| QMSS             | Packet DMA Does Not Update RX PS<br>Region Location Bit                                 | Usage Note 13 | Х   | Х       |          |         |     |

| QMSS             | Queue Proxy Access                                                                      | Usage Note 14 | Х   | Х       | Χ        | Х       | Х   |

| Power            | Initial Voltage Level Setting of CVDD Rail Power Supplies                               | Usage Note 17 | Х   | Х       | Х        | Х       | Х   |

| Debug            | DEBUGSS CTTBR ID Period Functionality Issue                                             | Usage Note 18 | Х   | Х       |          |         |     |

| Boot             | Boot Mode Change by Writing to DEVSTAT<br>Register Does Not Survive Warm Reset          | Usage Note 19 | Х   | Х       | Х        | Х       | Х   |

| Hyperlink        | HyperLink 0 and HyperLink1 PRIVIDs Not<br>Generated by the HyperLink IP                 | Usage Note 20 | Х   | Х       |          |         |     |

| USB              | USB EP15 Not Supported                                                                  | Usage Note 21 | Х   | Х       |          |         |     |

| Boot             | C66x Boot ROM Does Not Detect a Local<br>Reset Properly                                 | Usage Note 22 | Х   | Х       | Х        | Х       | Х   |

| Boot             | BOOTCOMPLETE Not Functional when ARM CorePac is a Boot Master                           | Usage Note 23 | Х   | Х       | Х        | Х       | Х   |

| Power            | Clock Alignment Issue When in Reset Isolation Mode                                      | Usage Note 24 | Х   | Х       | Х        | Х       | Х   |

| USB              | USB Hangs When Doing a Master Access to Reserved Space                                  | Usage Note 25 | Х   | Х       | Х        | Х       | Х   |

| 10GbE            | Device Hang if 10GbE PCS Registers are<br>Accessed After Performing a 10G Lane<br>Reset | Usage Note 27 | Х   | Х       | Х        |         |     |

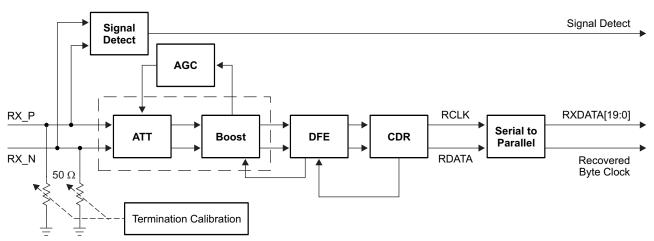

| SerDes           | SerDes Fails to Adapt RX BOOST Equalization                                             | Usage Note 28 | Х   | Х       | Х        | Х       | Х   |

# **Silicon Updates**

| Title Title                                                                                                                                                                              | Page |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| KeyStonell.BTS_errata_advisory.1 — Boot ROM Missed EMIF PHY Configuration Registers                                                                                                      | 12   |

| KeyStonell.BTS_errata_advisory.2 — Execution in Place (XIP) from NOR Flash on NOR XIP Does Not Work                                                                                      | 13   |

| KeyStonell.BTS_errata_advisory.3 — ARM L2 Latency is Not Set Correctly                                                                                                                   | 14   |

| KeyStonell.BTS_errata_advisory.4 — SRIO Boot Mode Packet DMA Cleanup Missing                                                                                                             | 15   |

| KeyStonell.BTS_errata_advisory.5 — Sync-Ethernet Push Event IO Control Tie-Off Incorrect                                                                                                 | 16   |

| KeyStonell.BTS_errata_advisory.8 — EMIF Boot (NOR flash) Mode Not Working When ARM Master Boot                                                                                           |      |

| KeyStonell.BTS_errata_advisory.9 — 1.4 GHz ARM is Not Supported                                                                                                                          | 18   |

| KeyStonell.BTS_errata_advisory.10 — DDR3A Lanes 5 and DDR3B Lane 8 Have PHY to PUB DFI Hold Time Failures                                                                                | 19   |

| KeyStonell.BTS_errata_advisory.13 — Corruption of Control Characters In SRIO Line Loopback Mode Issue                                                                                    |      |

| KeyStonell.BTS_errata_advisory.14 — HyperLink Temporary Blocking Issue                                                                                                                   |      |

| KeyStonell.BTS_errata_advisory.15 — RESETSTAT Signal Driven High Issue                                                                                                                   |      |

| KeyStonell.BTS_errata_advisory.16 — SRIO Control Symbols Are Sent More Often Than Required Issue                                                                                         |      |

| KeyStonell.BTS_errata_advisory.17 — System Reset Operation Disconnects SoC from CCS Issue                                                                                                |      |

| KeyStonell.BTS_errata_advisory.19 — ARM CorePac Powerdown and Hibernation Modes Not Supported                                                                                            |      |

| KeyStonell.BTS_errata_advisory.20 — False DDR3 Write ECC Error Reported Under Certain Conditions                                                                                         |      |

| KeyStonell.BTS_errata_advisory.21 — DDR3 Leveling issue                                                                                                                                  |      |

| KeyStonell.BTS_errata_advisory.22 — PCIE MSI/Legacy IRQ Does Not work for Root Complex                                                                                                   |      |

| KeyStonell.BTS_errata_advisory.23 — SES Port Should Only be Used for DDR3A Accesses                                                                                                      |      |

| KeyStonell.BTS_errata_advisory.28 — Descriptors Placed in PCIe Memory Space can Cause Problems                                                                                           |      |

| KeyStonell.BTS_errata_advisory.29 — 10GbE PCS Causes Data Corruption                                                                                                                     |      |

| KeyStonell.BTS_errata_advisory.30 — 10GbE PCB Channel Loss Limited to 20dB                                                                                                               |      |

| KeyStonell.BTS_errata_advisory.31 — HyperLink Channel Loss                                                                                                                               |      |

| KeyStonell.BTS_errata_advisory.33 — HyperLink Data Rate Limited to 40 Gbaud Issue                                                                                                        |      |

| KeyStonell.BTS_errata_advisory.34 — DDR3 Limited to Highest Data Rates Due to Possibility of PLL Instability During Temperature Changes After Startup                                    |      |

| KeyStonell.BTS_errata_advisory.35 — Restrictions on DDR3 PLL Configuration and DDR3nCLK to Eliminate                                                                                     |      |

| DDR3 Errors Due to PLL Dynamic Phase Offset                                                                                                                                              | 43   |

| TeraNet Hang                                                                                                                                                                             | 46   |

| KeyStonell.BTS_errata_advisory.37 — USB3.0 PHY Does Not Meet USB Specification: Rev 3.0 RX Jitter Tolerance Mask Across Non- Nominal Process                                             | 51   |

| KeyStonell.BTS_errata_advisory.38 — PCI-Express Hot Reset Not Handled During Boot                                                                                                        | _    |

| KeyStonell.BTS_errata_advisory.39 — CPSW Stall if Duplex Changes During Transmission                                                                                                     |      |

| KeyStonell.BTS_errata_advisory.40 — ROM: NAND Boot Failure When Booting Single Block Backup Images                                                                                       |      |

| KeyStonell.BTS_errata_advisory.41 — NAND Boot Failure With Bit Errors in ECC                                                                                                             |      |

| KeyStonell.BTS_errata_advisory.42 — ARM Ethernet Boot Reinitializes the Switch With Reset Isolation Enabled, Which May Cause Lockup                                                      |      |

| KeyStonell.BTS_errata_advisory.44 — SerDes RX Adapts to a BOOST Value of 0 and Cannot Move From a Value of 0                                                                             |      |

| KeyStonell.BTS_errata_advisory.45 — PCle link power states other than L0 are not supported on some Keystone II SOCs                                                                      |      |

| KeyStonell.BTS_errata_advisory.46 — Queue Diversion Failure                                                                                                                              |      |

| KeyStonell.BTS_errata_advisory.47 — SGMII, SRIO, Hyperlink, and PCIe Boot Failure                                                                                                        |      |

| KeyStonell.BTS_errata_usagenote.1 — SPI Boot Size Limitation, C66x Master Boot                                                                                                           |      |

| KeyStonell.BTS_errata_usagenote.1 — Gr / Boot Size Elimitation, Good Master Boot.  KeyStonell.BTS_errata_usagenote.2 — ARM Core Hangs if Timer is Accessed While ARM Core is in Wait-In- | 02   |

| Reset State                                                                                                                                                                              | 63   |

| KeyStonell.BTS_errata_usagenote.3 — Debug System (DebugSS) Trace Buffer EDMA via System Port Not Functional                                                                              | 64   |

| KeyStonell.BTS_errata_usagenote.4 — ARM Boot Can Fail When Interrupt Enabled                                                                                                             |      |

# Silicon Updates (continued)

| KeyStonell.BTS_errata_usagenote.5 — Boot fC Frequency Incorrect                                                  | 66         |

|------------------------------------------------------------------------------------------------------------------|------------|

| KeyStonell.BTS_errata_usagenote.6 — Access to DDR3 Without Configuring PHY Properly Can Cause Hang               | 67         |

| KeyStonell.BTS_errata_usagenote.7 — C66x CorePac and ARM CorePac AVS Rails                                       | 68         |

| KeyStonell.BTS_errata_usagenote.9 — Core Wake Up on RESET Usage Note                                             | 69         |

| KeyStonell.BTS_errata_usagenote.10 — fC Bus Hang After Master Reset Usage Note                                   | <b>7</b> 0 |

| KeyStonell.BTS_errata_usagenote.11 — Minimizing Main PLL Jitter Usage Note                                       | 71         |

| KeyStonell.BTS_errata_usagenote.13 — Packet DMA Does Not Update RX PS Region Location Bit Usage Note             | 72         |

|                                                                                                                  | 73         |

| KeyStonell.BTS_errata_usagenote.17 — Initial Voltage Level Setting of CVDD Rail Power Supplies Usage Note        | 74         |

| KeyStonell.BTS_errata_usagenote.18 — DEBUGSS CTTBR ID Period Functionality Issue                                 | 75         |

| KeyStonell.BTS_errata_usagenote.19 — Boot Mode Change by Writing to DEVSTAT Register Does Not Survive Warm Reset | 76         |

| KeyStonell.BTS_errata_usagenote.20 — HyperLink 0 and HyperLink1 PRIVIDs Not Generated by the HyperLink IP        | 77         |

| KeyStonell.BTS_errata_usagenote.21 — USB EP15 Not Supported                                                      | 78         |

| KeyStonell.BTS_errata_usagenote.22 — C66x Boot ROM Does Not Detect a Local Reset Properly                        | 79         |

| KeyStonell.BTS_errata_usagenote.23 — BOOTCOMPLETE Not Functional when ARM CorePac is a Boot Master               | 80         |

| KeyStonell.BTS_errata_usagenote.24 — Clock Alignment Issue When in Reset Isolation Mode                          | 81         |

| KeyStonell.BTS_errata_usagenote.25 — USB Hangs When Doing a Master Access to Reserved Space                      | 82         |

|                                                                                                                  | 83         |

| KeyStonell.BTS_errata_usagenote.28 — SerDes Fails to Adapt RX BOOST Equalization                                 | 84         |

# KeyStonell.BTS\_errata\_advisory.1

### **Boot ROM Missed EMIF PHY Configuration Registers**

#### Revision(s) Affected

1.0

#### **Details**

Boot ROM missed initializing some EMIF PHY Configuration registers.

On PG1.0 Boot ROM, the built-in DDR3 PHY configuration for the DWCPUB PHY does not include values needed for PHY Config. The following values are needed to support configuring the PHY registers:

- DDR3A\_PLLCR offset 0x00000018

DDR3A\_DSGCR offset 0x00000040

DDR3A\_ZQ0CR1 offset 0x00000184

DDR3A\_ZQ1CR1 offset 0x00000194

- DDR3A\_ZQ2CR1 offset 0x000001A4

DDR3A\_ZQ3CR1 offset 0x000001B4

#### Workaround

If the non-default values are required in these registers, a two stage boot must be used.

# KeyStonell.BTS\_errata\_advisory.2

Execution in Place (XIP) from NOR Flash on NOR XIP Does Not Work

Revision(s) Affected

1.0, 1.1, 2.0, 3.0, 3.1

**Details**

ARM cannot perform direct execution from a parallel NOR flash connected via ASYNC

EMIF.

On these devices, ARM cannot perform direct execution from a parallel NOR flash connected via ASYNC EMIF. Direct execution from a parallel NOR flash does not work as ARM always generates 64-byte cacheline wrap mode accesses to EMIF. This is irrespective of marking this memory region as Device or Strongly Ordered as confirmed by ARM. ASYNC EMIF does not support 64-byte cacheline wrap accesses and therefore generates a bus error on receiving it. This causes an abort to happen in ARM. The ARM is, however, able to read data from a parallel NOR flash connected via ASYNC EMIF.

Workaround

None. If code is stored on NOR flash, it must be copied from the NOR to another

memory area and executed from there.

# KeyStonell.BTS\_errata\_advisory.3

ARM L2 Latency is Not Set Correctly

Revision(s) Affected 1.0

**Details** ARM L2 Latency is not set correctly in the Boot ROM

In PG1.0 devices, the boot ROM did not change the default value of L2 latency in the L2 Control register. The default value is 0 (which means two cycles). The required value is

3 (which means 4 cycles).

Workaround Either use one of the C66x boot modes or the I<sup>2</sup>C or SPI boot mode in ARM master boot

mode which does not setup the ARM PLL. Once the boot is done, the PLL can be

changed and the latency setup can be programmed accordingly.

# KeyStonell.BTS\_errata\_advisory.4

SRIO Boot Mode Packet DMA Cleanup Missing

Revision(s) Affected 1.0

Details The issue is within the Boot ROM. In SRIO Boot Mode, the Packet DMA is not torn down

when the SRIO boot is complete.

On PG1.0 devices, in SRIO boot mode, the boot ROM did not perform the Packet DMA cleanup (the Packet DMA is not torn down) when the boot is complete. All queues are

emptied and the QM is torn down, but the Packet DMA is left up.

**Workaround** Before reconfiguration, the existing configuration should be torn down.

# KeyStonell.BTS\_errata\_advisory.5

# Sync-Ethernet Push Event IO Control Tie-Off Incorrect

Revision(s) Affected 1.0

Details The tie-off for IO control for the two Sync-Ethernet Push Events is connected incorrectly

in the design.

On PG1.0 devices, the tie-off for IO control for the two Sync-Ethernet Push Event (TSPUSHEVT0 (PPS Push Event from GPS for IEEE1588) and TSPUSHEVT1 (Push

Event from BCN for IEEE1588)) IOs is connected incorrectly in the design.

Consequence of this is that the TSPUSHEVT0 and TSPUSHEVT1 pads are being forced to outputs when not in reset, and thus **cannot** be selected as inputs. These pads are

functionally used as inputs.

Workaround None.

# KeyStonell.BTS\_errata\_advisory.8

EMIF Boot (NOR flash) Mode Not Working When ARM Master Boot

Revision(s) Affected 1.0

**Details** EMIF (NOR flash) boot does not work when ARM is the boot master.

Because ARM cannot perform direct execution from a parallel NOR flash connected via ASYNC EMIF the boot mode EMIF (NOR flash) on this version of the device does not work when ARM is the boot master. The boot failed because the ROM boot loader simply branched to an address in the NOR to execute code stored on the NOR. This was how boot mode works in later versions of the device because the ROM boot loader instead copies to the code image from the NOR to internal memory and then executes

the code copy.

Workaround Use C66x boot master if NOR flash boot is required.

# KeyStonell.BTS\_errata\_advisory.9

1.4 GHz ARM is Not Supported

Revision(s) Affected 1.0

**Details** 1.4 GHz ARM is not supported silicon revision listed in the table.

The ARM cannot fully function at 1.4 GHz with core power supplies of 900 mV nominal

voltage.

Workaround Run the ARM at a 1.2 GHz.

# KeyStonell.BTS\_errata\_advisory.10

#### DDR3A Lanes 5 and DDR3B Lane 8 Have PHY to PUB DFI Hold Time Failures

Revision(s) Affected

1.0

**Details**

### DDR3A Bit Errors in Data Byte Lane 5

It has been observed that operating DDR3A in 64-bit mode results in occasional read errors. The problem is observed across all frequencies of operation.

The read errors occur across byte lane 5 of the DDR3A interface due to hold time violations on the DFI interface between the PHY Utility Block and SDRAM PHY on this specific byte lane. Since the hold violations are only on byte lane 5, this issue impacts only 64-bit DDR3A operation and not 32-bit or 16-bit DDR3A operations.

Table 5. DDR3A

| 72 bit with ECC    | Nonfunctional |

|--------------------|---------------|

| 64 bit without ECC | Nonfunctional |

| 36 bit with ECC    | Functional    |

| 32 bit without ECC | Functional    |

| 16 bit without ECC | Functional    |

#### Workaround

The only stable work around available at this time is to operate the DDR3A interface in 32-bit or 16-bit mode. These configurations would ensure the faulty byte lane is never activated.

#### **Details**

#### DDR3B Bit Errors in ECC Byte Lane

It has been observed that error correction is currently nonfunctional on the DDR3B interface. Turning on ECC during DDR3B operation results in occasional read errors as a result of miscalculated ECC values.

Table 6. DDR3B

| 72 bit with ECC    | Nonfunctional |  |

|--------------------|---------------|--|

| 64 bit without ECC | Functional    |  |

| 36 bit with ECC    | Nonfunctional |  |

| 32 bit without ECC | Functional    |  |

| 16 bit without ECC | Functional    |  |

#### Workaround

The only stable work around available at this time is to operate DDR3B interface in non ECC mode. This configuration would ensure the faulty byte lane is never activated.

#### KeyStonell.BTS\_errata\_advisory.13

#### Corruption of Control Characters In SRIO Line Loopback Mode Issue

Revision(s) Affected

1.0, 1.1, 2.0, 3.0, 3.1

**Details**

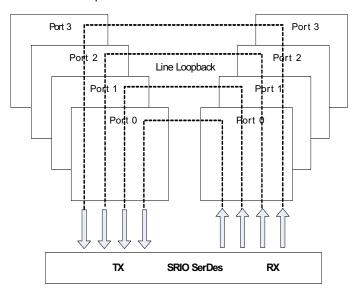

The SRIO physical layer is configured in line-loopback mode on a per-port basis, by setting the LLB\_EN bit in PLM\_SP(n)\_IMP\_SPEC\_CTL register. In line-loopback mode, the data from the SerDes receiver is looped back to the SerDes transmitter. Figure 2 shows the line loopback from SerDes RX to SerDes TX.

Figure 2. SRIO SerDes in Loopback Mode

The port does not provide any clock compensation when line loopback is enabled. The transmit clock must be externally synchronized with the receive clock. There is only a small FIFO that can compensate for PLL jitter or wander. Hence, correct operation of line loopback requires that the link partners use the same reference clock for the SRIO physical layer, in order to avoid overruns or underruns due to clock frequency mismatch between the link partners. As a result, line loopback mode is generally restricted to validation and qualification of board signal integrity in a lab environment.

When line loopback is enabled on one or more SRIO ports, any valid 10b code group that decodes to an illegal control character as defined by the RapidIO Specification (Revision 2.1) and whose most significant bit is 0, will be corrupted on transmission. This issue can be summarized as follows:

- 10b code group -> Legal control character -> No problem

- 10b code group -> Illegal control character and most significant bit is 0 -> Corruption

Workaround

Instead of using PRBS sequences, users can qualify boards by using RapidIO-compliant data on the link and monitoring either per-lane error counters or port-level error counters. RapidIO-compliant data is less stressful than PRBS sequences, as the RapidIO-compliant 10b data has shorter 0s and 1s run lengths than PRBS sequences. Hence, RapidIO-compliant data represent a more accurate stimulus for this test. This should be acceptable for users whose RapidIO links are of short reach, which can be either 20 cm + 1 connector or 30 cm without a connector.

# KeyStonell.BTS\_errata\_advisory.14

#### HyperLink Temporary Blocking Issue

**Revision(s) Affected** 1.0, 1.1, 2.0, 3.0, 3.1

Details A HyperLink temporary blocking condition can exist when a local device is reading from

a remote device so heavily that the responses from the remote device keep the response path continuously busy. Because responses have a higher priority than outgoing commands, the remote device is temporarily unable to send commands to the

local device.

Workaround 1: Use a push messaging model instead of pull.

Workaround 2: If a pull model is needed, schedule breaks so the return path is not continuously busy.

# KeyStonell.BTS\_errata\_advisory.15

#### **RESETSTAT** Signal Driven High Issue

**Revision(s) Affected** 1.0, 1.1, 2.0, 3.0, 3.1

Details The RESETSTAT output signal should be driven low when a reset is applied and held

low until the reset cycle is complete. If the device is using power sequencing where the 1.8 V (DVDD18) is present before the AVS core voltage (CVDD), the RESETSTAT signal may be driven high erroneously during the time between when DVDD18 is present

and the CVDD is present.

Workaround One workaround is to use the CVDD before DVDD18 in the power sequencing. An

alternative workaround is to ignore the RESETSTAT signal if the CVDD is not present

during the power sequencing.

# KeyStonell.BTS\_errata\_advisory.16

#### SRIO Control Symbols Are Sent More Often Than Required Issue

Revision(s) Affected

1.0, 1.1, 2.0, 3.0, 3.1

**Details**

Control symbols are SRIO physical layer message elements used to manage link maintenance, packet delimiting, packet acknowledgment, error reporting, and error recovery. Control symbols are used to manage the flow of transactions in the SRIO physical interconnect. The SRIO input status control symbols communicate the status of the physical link and packets in flight between the two SRIO link partners.

The bandwidth of the SRIO link is reduced because status control symbols are sent more often than required. Worst case impact is a 2.73 percent reduction in bandwidth for a 1x port operating at 1.25 Gbaud. This impact is reduced to 0.1 percent for a 4x port operating at 5 Gbaud. More details about this impact on various lane speed and port configurations can be found in Table 7.

**Table 7. Impact on Various Lane Speeds**

|                    | Percentage of Bandwidth Reduction |         |         |

|--------------------|-----------------------------------|---------|---------|

| Lane Speed (Gbaud) | 1x Port                           | 2x Port | 4x Port |

| 1.25               | 2.73                              | 1.37    | 0.68    |

| 2.5                | 1.17                              | 0.59    | 0.29    |

| 3.125              | 0.86                              | 0.43    | 0.21    |

| 5.0                | 0.39                              | 0.20    | 0.10    |

Workaround

None

# KeyStonell.BTS\_errata\_advisory.17

#### System Reset Operation Disconnects SoC from CCS Issue

Revision(s) Affected

1.0, 1.1, 2.0, 3.0, 3.1

**Details**

CCS connection to targets will fail after system reset issued via CCS. CCS connection to targets will also fail after RESET reset of the device. A system reset, issued from CCS or by the RESET pin, can cause power reset to all C66x Corepacs and can cause the hardware states of debug logic (including hardware breakpoints) to get cleared. The result is that any existing CCS connection to those targets will get corrupted, terminating further access to the target.

Workaround 1:

A new configuration option called Domain Power Loss Mode is added in the CCS target configuration for enabling the debug software to detect and handle the power loss event automatically.

To enable this option, in the CCS target configuration window, click on the sub-path of ICEPICK\_D for each individual C66x Corepac. Then click on the property option **Domain Power Loss Mode** and select **Auto**.

The support for this new option will be released in the emupack update v5.0.586.0 or newer, patched to CCS5.1 GA.

Workaround 2:

Before issuing a system reset, disconnect CCS from all DSP targets, issue the system reset, then reconnect CCS to the targets to continue debug operations.

# KeyStonell.BTS\_errata\_advisory.19

ARM CorePac Powerdown and Hibernation Modes Not Supported

Revision(s) Affected 1.0, 1.1

Details ARM CorePac powerdown mode (SoC PSC initiated clock off or power off request) is not

supported.

Workaround None

#### KeyStonell.BTS\_errata\_advisory.20

#### False DDR3 Write ECC Error Reported Under Certain Conditions

Revision(s) Affected

1.0, 1.1, 2.0, 3.0, 3.1

**Problem Summary:**

In the event that the read-modify-write (RMW) ECC feature for DDR3 is not supported or disabled, an L1D or L2 block writeback or writeback invalidate operation to ECC protected DDR3 space will flag a DDR3 write ECC error, even though neither the data nor the ECC values stored in the SDRAM will be corrupted.

**Details**

The write ECC error interrupt can be enabled by setting the WR ECC ERR SYS bit in the Interrupt Enable Set Register (IRQSTATUS\_ SET\_SYS) of the DDR3 controller.

Under normal conditions, a write access performed within the ECC protected address range to a 64-bit aligned address with a byte count that is 64-bit quanta is not expected to flag a write ECC error interrupt. The C66x cache controller always operates on whole cache lines, which are 128 bytes for the L2 cache and 64 bytes for L1D cache. However, a block writeback or writeback invalidate always generates a bounding single byte write (with its byte enables disabled) to the last address in that block. This single byte write violates both the alignment and quanta conditions causing the DDR3 controller to flag a write ECC error in the Interrupt Raw Status Register (IRQSTATUS\_RAW\_SYS) register. Since this bounding write is sent with its byte enables disabled, it does not actually reach the DDR memory and does not corrupt the stored data or ECC values. The write ECC error is thus a spurious error since no data or ECC value is actually corrupted. It should be noted that the DDR3 controller, in response to this sub-quanta write (the bounding single byte write), will report an error on an internal status line to the CPU that executed the writeback. This error status flags the MDMA error interrupt to the CPU and is interpreted as an MDMA data error (the STAT field in the CPU's MDMA Bus Error Register will be set to 0x4).

NOTE: 1: Since no bounding writes are generated with global writeback or global writeback invalidate operations, this issue is limited only to block writebacks to ECC protected region.

NOTE: 2: If the MDMA error flagged by a block coherence operation is followed by a true MDMA error flagged by a master executing a direct sub-quanta write, only the first MDMA error will be captured. Software must clear an MDMA error as soon as possible in order for future errors to be captured.

Workaround 1

The problem can be resolved by enabling the read-modify-write ECC feature for DDR3 (set RMW EN=1 in the ECCCTL register of the DDR3 memory controller). The RMW feature is specifically designed to handle sub-quanta/non-aligned accesses to ECC protected space. With RMW enabled the bounding single byte write will not violate any quanta/alignment requirements and thus will not flag a write ECC error.

Silicon rev1.0 and 1.1 of this device do not support RMW. Silicon rev2.0 supports RMW.

Workarounds 2 and 3 should be explored if RMW is not available or not used.

Workaround 2

In order to differentiate a false write ECC error from a true error generated by alignment/quanta violations, the system should keep track of block writeback/writeback invalidate operations to the ECC protected memory space. If a write ECC error is confirmed for that operation, it can be safely ignored. There is only a single DDR3 error interrupt that will have to be processed by one of the C66x cores. Therefore, some special mechanism will be required for the system to keep track of which core performed the block writeback that caused the error. This mechanism may involve checking for the data error reported in the MDMA Bus Error Register.

NOTE: 3: A system must satisfy the alignment/quanta conditions so a true write ECC error is not expected and such errors should be isolated and removed as part of system software evaluation.

NOTE: 4: The system software must clear the write ECC error and MDMA error before they can be re-triggered by any successive error conditions. It should be noted that a race condition can exist if a subsequent ECC error (real or false) or MDMA error interrupt is triggered before the previous interrupt is cleared.

#### Workaround 3

A global coherence operation can be performed instead of a block operation. It should be noted that a global operation can possibly operate on more cache lines than the block operation, causing a larger than necessary cycle overhead and negatively impact memory system performance.

FAQ:

Q: The C66x CorePac will receive an MDMA error in response to the DDR3 ECC error. Other masters may also see the DDR3 ECC error when transactions they have sent result in the error. How do these masters respond to a DDR3 ECC error?

A: The responses of the C66x CorePac, ARM CorePac, and other masters to the nonzero values returned on rstatus and sstatus due to DDR3 ECC errors are summarized in Table 8.

Table 8. Master Behavior in Response to sstatus/rstatus Flagged Due to DDR3 ECC Errors

| Master                                          | Bus Error<br>Returned | Error Status Captured                                                                                                                                                                                                                                                                                            | Alarm Notification                                                                                                                                                                                               |

|-------------------------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C66x CorePac                                    | sstatus,<br>rstatus   | Error status captured in the STAT field in the C66x CorePac's MDMA Bus Error Register will be set to 0x4.                                                                                                                                                                                                        | The C66x CorePac's MDMA error interrupt is asserted.                                                                                                                                                             |

| ARM CorePac                                     | sstatus,<br>rstatus   | Details on the exception are captured in the CP15 registers: Data Fault Status Register (DFSR), Instruction Fault Status Register (IFSR) or Auxiliary Data Fault Status Register (ADFSR). The address that generated the abort can be seen by reading Data Fault Address Register (DFAR) for synchronous aborts. | The ARM CorePac will trigger an external abort exception. They are disabled by default and should be enabled via the CPSR.A bit (Current Program Status Register).                                               |

| PCIe                                            | sstatus,<br>rstatus   | Interrupts are not generated and error status is not logged.                                                                                                                                                                                                                                                     | PCIe returns completion abort to requestor only for rstatus error. No completion abort is returned for a write error (sstatus).                                                                                  |

| EDMA TC                                         | sstatus,<br>rstatus   | BUSERR and ERRDET registers capture the error information. The transfer of data from source to destination happens irrespective of error.                                                                                                                                                                        | Error interrupt is generated if enabled within EDMA.                                                                                                                                                             |

| Multicore Navigator<br>Infrastructure<br>PktDMA | sstatus,<br>rstatus   | Error status is not logged.                                                                                                                                                                                                                                                                                      | Error interrupt is not reported                                                                                                                                                                                  |

| TSIP                                            | sstatus,<br>rstatus   | Errors will be stored in the channels' interrupt queue along with the error codes.                                                                                                                                                                                                                               | TSIP asserts an error event (TSIPx_ERRINTn) when an error is queued for channel 'n'. CorePac[n] will receive TSIPx_ERRINTn.                                                                                      |

| SRIO                                            | sstatus,<br>rstatus   | Error responses set a bit in the AMU_INT_ICSR register based on the CPRIVID of the transactions. The RIO_AMU_ERR_CAPT0, RIO_AMU_ERR_CAPT1 registers will contain the address of the non-posted transactions that failed along with the CPRIVID and CMSTID.                                                       | Each bit can be routed by software configuration through the Interrupt Condition Routing Register (ICRR) to a specific ARM or C66x CorePac for error handling. See the device data manual for interrupt mapping. |

# Table 8. Master Behavior in Response to sstatus/rstatus Flagged Due to DDR3 ECC Errors (continued)

| Master    | Bus Error<br>Returned               | Error Status Captured                                                                                             | Alarm Notification                                                                                                                               |

|-----------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| HyperLink | sstatus,<br>rstatus                 | When the serial link is active HyperLink will pass the rstatus. Rstatus is will be that of the remote slave read. | HyperLink Error interrupt (HyperLink_INT or VUSR_INT) are generated when error is received and are provided to CorePacs as secondary interrupts. |

| 10GbE     | sstatus,<br>rstatus are<br>not used | NA                                                                                                                | NA                                                                                                                                               |

**NOTE:** Check your device data manual to see which masters are applicable.

# KeyStonell.BTS\_errata\_advisory.21

#### DDR3 Leveling issue

#### Revision(s) Affected

1.0, 1.1

#### **Details**

DDR Read/Write errors are reported after DDR initialization for <1% of power-on resets. When executing UBOOT from the MCSDK, this results in DDR POST (Power On Self Test) failure.

Sometimes DDR initialization fails with leveling errors (reported in DDR PHY status registers). Once the leveling errors are reported, DDR read/write operations fail. This issue happens only during initialization time and cannot occur during runtime. This issue occurs irrespective of the operating frequency of the device and is also independent of the operating frequency of the DDR. This issue is applicable for both DDR3A and DDR3B. ROM Boot modes supporting initialization of, and booting to DDR can fail due to this issue. Below is the list of boot modes for which ROM Bootloader performs DDR configuration (only if boot image is required to be stored in DDR):

- I<sub>2</sub>C Master

- SPI

- EMIF NOR

- EMIF NAND

The root cause is identified to an issue that happens after the very first DDR3 PHY initialization, this first initialization happens directly from Power-on reset. The issue occurs because the clocking requirements of the DDR3 PHY are not met on the first initialization, this happens because the DDR3A and DDR3B SoC PLLs are not yet programmed to provide the requisite clock. There is a ratio requirement between the DDR3A/B PHY clocks and the core configuration clock, such that the core configuration clock must be less than or equal to the PHY clock. These clocks are asynchronous and the PHY support an asynchronous FIFO scheme with limited depth on the PHY clock domain. If the ratio requirement is not met then FIFO can overflow. This would mean that the configuration data for the PHY may be lost during the initialization sequence. Experiments have proven that if we apply Hard Reset once the clocking has been set up correctly, the issue is resolved.

#### Workarounds

DDR read/write failures can be avoided by checking the DDR PHY status register for any Leveling errors at the end of DDR PHY Initialization. For boot modes using DDR, the workarounds below can be used as a part of second-stage boot only. Once the leveling errors are detected, one of the following workarounds can be used.

#### Workaround 1

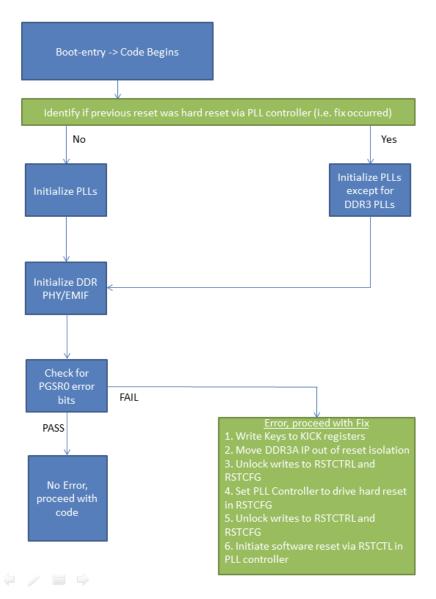

This workaround is to detect this error in the PHY Init function and apply Hard Reset to the device. Hard Reset of the device can be done by performing the following:

Software Reset using RSTCTRL register in PLL Controller

Below is the logical explanation of the flow where the above Reset needs to be applied.

Figure 3. Software Reset Using the RSTCTRL Register

BLUE colored blocks show the normal execution while the GREEN colored blocks show the changes. The "Error, proceed with Fix" block is the block which explains the steps that need to be followed to apply the Software Reset using RSTCTRL register. The steps are mentioned for DDR3A. The same steps need to be used for DDR3B also.

#### Below is the source code for reference:

```

// Check PGSR0 Error bits of DDR3 PHY

tmp = __read(DDR3A_DDRPHY_BASE + DDRPHY_PGSR0_OFFSET);

if (((tmp & 0x00000E00) != 0x00000E00) || ((tmp & 0x0FE00000) != 0)) {

// Write Keys to KICK registers to enable writes to registers in boot config space

__write(KEYSTONE_KICK0_MAGIC, KEYSTONE_KICK0);

__write(KEYSTONE_KICK1_MAGIC, KEYSTONE_KICK1);

// Move DDR3A Peripheral out of reset isolation by setting MDCTL23[12] = 0

tmp = read(PSC BASE + MDCTRL23 OFFSET);

tmp &= ~(0x1000);

__write(tmp, PSC_BASE + MDCTRL23_OFFSET);

// Write 0x5A69 Key to RSTCTRL[15:0] to unlock writes to RSTCTRL and RSTCFG

tmp = __read(PLL_CNTRL_BASE + MAIN_PLL_CTRL_RSTCTRL_OFFSET);

tmp &= ~(0xFFFF);

tmp |= 0x5A69;

write(tmp, PLL_CNTRL_BASE + MAIN_PLL_CTRL_RSTCTRL_OFFSET);

// Set PLL Controller to drive hard reset on SW trigger by setting RSTCFG[13] = 0

tmp = read(PLL CNTRL BASE + MAIN PLL CTRL RSTCFG OFFSET);

tmp \&= ^{(0x2000)};

tmp = 0x0000;

__write(tmp, PLL_CNTRL_BASE + MAIN_PLL_CTRL_RSTCFG_OFFSET);

// Write 0x5A69 Key to RSTCTRL[15:0] to unlock writes to RSTCTRL and RSTCFG

tmp = read(PLL CNTRL BASE + MAIN PLL CTRL RSTCTRL OFFSET);

tmp &= ^{\sim}(0xFFFF);

tmp |= 0x5A69:

__write(tmp, PLL_CNTRL_BASE + MAIN_PLL_CTRL_RSTCTRL_OFFSET);

// Write RSTCTRL[16] = 0 to initiate software reset via PLL controller

tmp = __ read(PLL_CNTRL_BASE + MAIN_PLL_CTRL_RSTCTRL_OFFSET);

tmp &= ~(0x10000);

tmp = 0x000000;

__write(tmp, PLL_CNTRL_BASE + MAIN_PLL_CTRL_RSTCTRL_OFFSET);

>> PLL Controller should now initiate Hard Reset

```

Figure 4. Reset Source Code

Another GREEN block shown in the above block diagram is normal sequence where U-Boot identifies whether the previous reset is Hard Reset or not and skips the PLL configuration as Hard Reset does not reset the PLLs. Execution can read the RSTYPE register bit field PLLCTRLRST to identify whether the previous reset is the Software Reset initiated by RSTCTRL register in PLL controller or not.

In ARM-side implementation, detection of the leveling error and applying Reset needs to be done in U-Boot. Board.c file can be modified to apply this workaround. Below are the functions that need to be modified:

- board\_early\_init (function) Identify previous reset type and determine if PLLs should be initialized

- dram\_init (function) Detection of PGSR0 error and applying Software Reset steps as shown above

#### **CCS** Reset using Emulator

During development environment using CCS if the leveling error comes up on the DDR configuration then CCS Emulation Reset "System Reset" can be used to apply Hard Reset to SoC.

Once the above reset is applied and booting is performed again, the boot code needs to identify whether it is the Hard Reset OR it is 'Power-on reset' (i.e., POR or RESETFULL). Once it is identified as a Hard Reset, the boot code needs to proceed with usual sequence without a DDR PLL initialization, and perform the DDR PHY configuration. During this second DDR PHY initialization after the Hard Reset the Leveling errors will not occur.

#### Workaround 2

If Workaround#1 has some other implications at the board level OR system level then this workaround can be used. This workaround is to detect this error in the PHY Init function and apply RESETFULL or POR to the device. Due to RESETFULL or POR this workaround has no surety of the reoccurrence of the same issue again, but it goes through the same probability of the occurrence (less than 1%) of the issue. Therefore, the likelihood of this issue re-occurring is less. At this point testing has not shown this issue occurring on two consecutive RESETFULL or POR.

This method can also be used when utilizing the DDR initialization option within the ROM boot loader. If the boot is determined to fail by the external host, then a new RESETFULL or POR should be applied to the device and the boot sequence re-started.

# KeyStonell.BTS\_errata\_advisory.22

#### PCIE MSI/Legacy IRQ Does Not work for Root Complex

Revision(s) Affected

1.0, 1.1, 2.0, 3.0, 3.1

**Details**

While testing the AER PCIE error handling and error recovery Linux driver software on KeyStone II EVM, it was found that only error interrupt #12 is raised. An unsupported request error is simulated by generating transaction to an EP with an address not in the BAR. The error is detected by Root complex.

As per PCIE spec 2.0, section 6.2.6, MSI/Legacy error interrupt to be raised as well platform specific interrupt. Currently, only platform specific interrupt (INT #12) is raised. AER driver depends on Legacy/MSI IRQ and can't function without this. This is the

standard PCI driver in Linux to handle Error and do recovery.

Workaround

None

#### KeyStonell.BTS\_errata\_advisory.23

#### SES Port Should Only be Used for DDR3A Accesses

#### Revision(s) Affected

1.0, 1.1

**Details**

This errata is to notify about usage of SES only for DDR3A accesses.

MSMC provides two system access ports, SMS and SES. The SMS port provides direct access to MSMC SRAM. The SMS port resides at system addresses 0x0C000000 - 0x0CFFFFF. The SES port provides access to both DDR3A and MSMC SRAM. The SES port resides at system address 0x80000000 - 0xFFFFFFF. By default, MSMC directs access via SES to the DDR3A EMIF. Thus, after reset, system addresses 0x80000000 - 0xFFFFFFFF correspond to DDR3A. Using SES MPAX registers, programs can redirect some or all accesses in this range to MSMC SRAM.

The SES processes requests to MSMC SRAM and DDR3A internally on separate paths. However, responses for read and write commands to SES must merge into a common path before returning to the system. In particular, write commands must return a write status (sstatus) to indicate that the write completed, and MSMC must merge the write status streams from MSMC SRAM requests and DDR3A requests into a single stream returning to the system.

The SES prioritizes responses from MSMC RAM over responses from DDR3A. When SES is heavily loaded with a mixture of requests to MSMC SRAM and DDR3A, responses returned from MSMC SRAM will delay responses from DDR3A. An extended series of delays will eventually fill DDR3A's response pipeline.

When the DDR3A response pipeline fills, it incorrectly drops write responses (sstatus) for write requests from master ID 0x52 (sid = 0x52). MSMC uses this master ID internally for cache coherence operations. BCP DIO1 also uses this master ID.

The dropped write responses lead to deadlock in one of two ways:

- Dropped write status for coherence writes causes the coherence machinery to stall indefinitely waiting for acknowledgement of its write.

- Dropped write status for BCP\_DIO1 writes causes BCP to stall waiting for its outstanding writes to complete.

#### Workaround

An example scenario that could lead to a configuration triggering this errata is to use onchip memory instead of off-chip to improve performance. In this scenario, both XMC and SES MPAX have aliases to MSMC SRAM in order to make the addressing transparent to application.

User must avoid aliased addresses on SES port by system masters

- Remove SES MPAX aliasing to MSMC.

- Consequently, any SW configuring any system master (eg., EDMAs) must translate aliased DDR3A addresses to global physical MSMC addresses (0x0c000000) such that they go through the SMS MPAX table instead of SES MPAX.

For example, application has 0x80000000 => 0x0c0000000 in both SES and XMC. The SES alias must be removed. Thus, the software must translate 0x80000000 to 0x0c0000000 then directly provide the 0x0c000000 address to the EDMAs. Due to the internal workings of the SoC, this causes the SoC to present the addresses to the SMS instead of SES which avoids the errata.

#### KeyStonell.BTS\_errata\_advisory.28

#### Descriptors Placed in PCIe Memory Space can Cause Problems

Revision(s) Affected

1.0, 1.1, 2.0, 3.0, 3.1

**Problem Summary:**

Packet DMA can generate write transactions with partial byte enables when trying to access descriptors. This can cause problems if the descriptors are stored in PCIe memory space since PCIe cannot handle partial byte enables. Here, *partial byte enables* means that the transactions are accessing memory that is not a full 32-bit word.

**Details**

Packet DMA can sometimes generate write transactions with partial byte enables asserted when trying to access descriptors. This can cause problems if the descriptors are placed in PCIe memory space since PCIe does not support transaction requests with partial byte enables. Such a transaction will corrupt the PCIe module's internal state machine and in turn corrupt the payload. This issue does not impact Packet DMA access to data buffers, only to descriptors since all byte enables are asserted in transactions involving data buffers. Thus, the data buffers may be stored anywhere including in PCIe memory space.

Workaround

As long as host-mode descriptors are used and these descriptors are located in a memory space that can properly handle partial byte enables (such as L2 SRAM, DDR3 or MSMC), the issue will not affect Packet DMA accesses to PCIe memory space. As mentioned earlier, data buffers can be stored in PCIe memory space without any problems.

#### KeyStonell.BTS\_errata\_advisory.29

#### 10GbE PCS Causes Data Corruption

Revision(s) Affected

1.0, 1.1, 2.0, 3.0, 3.1

**Problem Summary:**

The 10GbE Physical Coding Sublayer (PCS) used in the 10GbE interface may corrupt its

output data upon initialization.

**Details**

Upon initial synchronization to an incoming data stream, the 10G PCS may not configure itself correctly. Due to this incorrect configuration, the incoming data from the receive port will be corrupted before it is sent to subsequent blocks in the data path. As this issue occurs during initialization, if for a synchronization event the PCS is initialized correctly then data corruption does not occur. If the issue occurs, the data corruption can be seen when the PCS reports PCS block errors or in packet loss at the user space

software.

Workaround

PG1.X-PG2.0-PG3.0:

The user may detect the PCS-R corrupt state when packet loss is observed. Due to the conditions explained in Usage Note #27, a read of the hiber or block error fields in the PCS-R RX Status register may cause a VBUS lock. Thus these fields may not be used to detect the corrupt state. When the corrupt state is detected, the user can assert and then deassert the corresponding Serdes signal detect. This signal detect reset forces the RX to re-adapt to the incoming data, and causes an interruption to the datastream to the PCS. This causes the PCS to resynchronize. This workaround is currently implemented in the latest 10GbE Linux drivers (since MCSDK 3.0.4).

PG3 0:

PG3.0 devices have fixed the issue described in Usage Note #27. Due to this design improvement, users may now detect the corrupt state by reading the PCS-R RX Status Register's hiber and block errors fields. This means that the PCS-R may be reinitialized and brought to a healthy state prior to packet loss.

# KeyStonell.BTS\_errata\_advisory.30

#### 10GbE PCB Channel Loss Limited to 20dB

Revision(s) Affected

1.0, 1.1, 2.0, 3.0, 3.1

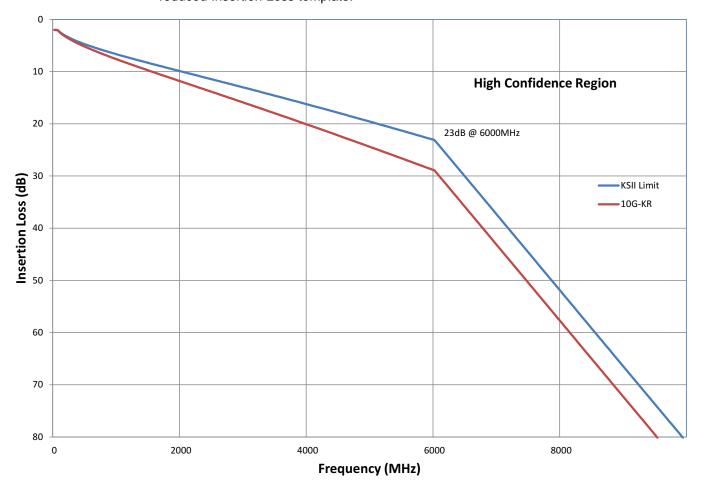

**Details**

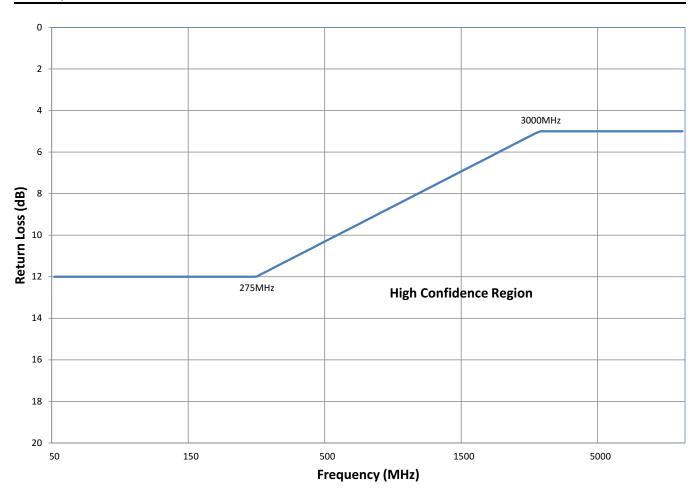

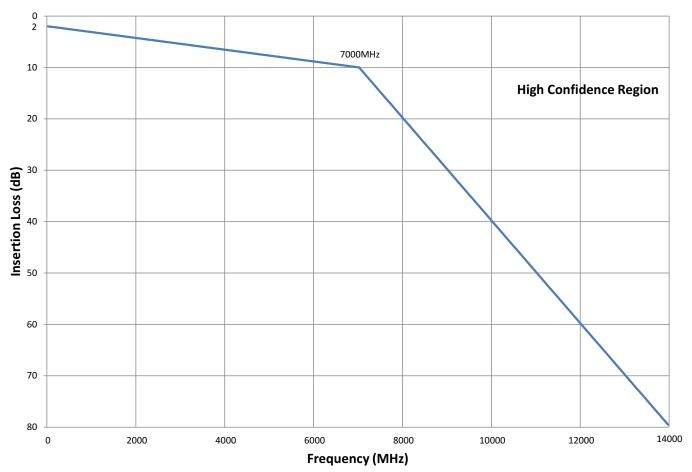

Device characterization has shown that bit error rate performance consistent with the 10GbE-KR standard as published in IEEE 802.3-2008 Annex 69B cannot be met across all device operating extremes. Production devices do operate at the required error rate across all rated operating conditions of voltage and temperature when the channel insertion loss is limited to 20dB at the Nyquist rate of 5.15625GHz. The figure below shows the Insertion Loss template from IEEE 802.3-2008 Annex 69B as well as the reduced Insertion Loss template.

Characterization has shown that channels must also be compliant with the Return Loss template contained in the IEEE 802.3-2008 Annex 69B specification without modification. This is shown below for convenience.

Workaround None.

# $KeyStonell.BTS\_errata\_advisory.31$

## HyperLink Channel Loss

Revision(s) Affected

1.0, 1.1, 2.0, 3.0, 3.1

**Details**

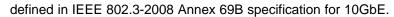

Device characterization has shown that expected bit error rate performance can only be met on layouts that meet constrained channel loss metrics. These can be examined by generating Insertion Loss and Return Loss graphs where loss is plotted versus frequency. Insertion Loss and Return Loss can be estimated during PCB layout using a 3D simulation tool. Insertion Loss and Return Loss should also be measured on early prototypes using a Vector Network Analyzer (VNA). Multiple PCB construction and layout enhancement techniques must be combined to achieve these channel performance requirements as stated in the KeyStone II SERDES User Guide.

An Insertion Loss measurement provides a composite view of the channel's loss versus frequency. Since HyperLink is a short-reach interface, channel loss is limited. Also, due to the high data rate, the Insertion Loss must be monotonic and without discontinuities that would degrade receiver operation. The template shown below provides Insertion Loss limits that will result in a robust channel. This template must be met for the entire channel from transmitter to receiver including the series capacitors.

Device characterization has also shown that channels should be compliant with the Return Loss template shown below. The Return Loss measurement indicates the amount of energy reflected back to the source which is not available to the receiver. Impedance variation in the channel will cause reflected energy that can cause this template to be violated. Careful attention to PCB construction and layout must be followed to meet this requirement. This template must be met for the entire channel from transmitter to receiver including the series capacitors. Note that this is the same template

Workaround

None.

# KeyStonell.BTS\_errata\_advisory.33

HyperLink Data Rate Limited to 40 Gbaud Issue

**Revision(s) Affected:** 1.0, 1.1, 2.0, 3.0, 3.1

**Details:** The HyperLink interface is currently limited to a maximum transfer rate of 10 Gbaud per

lane (40 Gbaud for four lanes) due to a SerDes PLL limitation.

# KeyStonell.BTS\_errata\_advisory.34

DDR3 Limited to Highest Data Rates Due to Possibility of PLL Instability During Temperature Changes After Startup